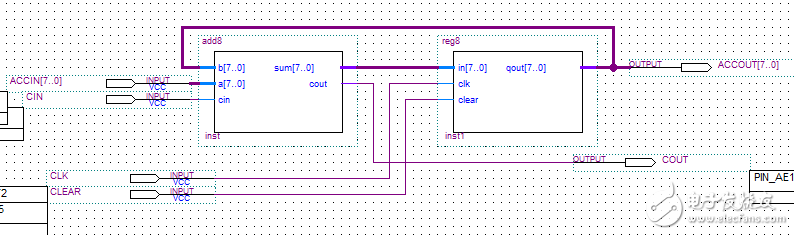

设计了一个8位acc累加器,为什么无法从零开始累加呢?

时间:10-02

整理:3721RD

点击:

8位全加器。add8.v

module add8(sum,cout,b,a,cin);

input[7:0] a/*synthesis keep*/,b/*synthesis keep*/;

input cin; output[7:0] sum/*synthesis keep*/;

output cout;

assign {cout,sum}=a+b+cin;

endmodule

8位寄存器。reg.v

module reg8(qout,in,clk,clear);

input[7:0] in/*synthesis keep*/;

input clk,clear;

output reg[7:0] qout/*synthesis keep*/;

always @ (posedge clk or posedge clear)

begin

if(clear)qout<=0;

else qout<=in;

end

endmodule

请问:设计出来的累加器只能从120开始累加,无法从零开始累加,就算是clear以后还是如此。要怎么把起始值设成零呢?

谢谢!~~

module add8(sum,cout,b,a,cin);

input[7:0] a/*synthesis keep*/,b/*synthesis keep*/;

input cin; output[7:0] sum/*synthesis keep*/;

output cout;

assign {cout,sum}=a+b+cin;

endmodule

8位寄存器。reg.v

module reg8(qout,in,clk,clear);

input[7:0] in/*synthesis keep*/;

input clk,clear;

output reg[7:0] qout/*synthesis keep*/;

always @ (posedge clk or posedge clear)

begin

if(clear)qout<=0;

else qout<=in;

end

endmodule

请问:设计出来的累加器只能从120开始累加,无法从零开始累加,就算是clear以后还是如此。要怎么把起始值设成零呢?

谢谢!~~

acc.v

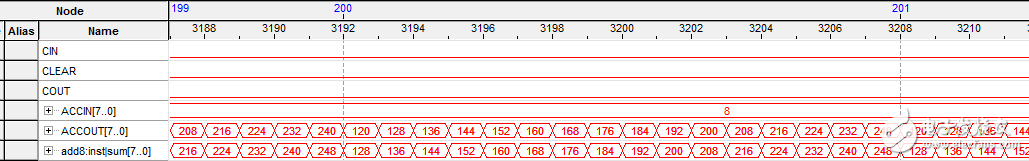

signal tap的截图

模电和模数都重要啊~~~~~~~