关于XILINX多片DDR2的硬件设计和MIG

时间:10-02

整理:3721RD

点击:

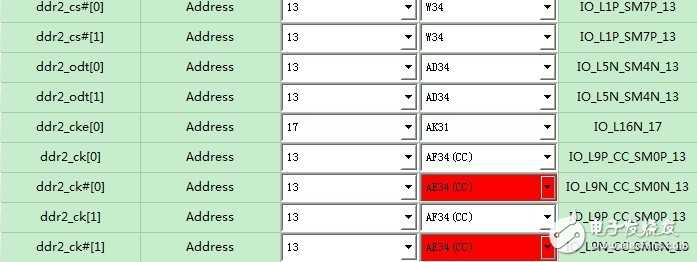

最近在做FPGA板子用了两片16位的FPGA,在MIG中发现ODT 和CK CS等信号需要分别连接到FPGA。如下图,是我在MIG中设置的问题吗?还是xilinx DDR2 MIG就要求这么做?

设置的 问题

我看了一些官方的设计也是需要分别连接的

cs应该可以直接拉死的,在设置里头有的,ck和odt好像是现在做了约束了,core gen必须要检查到管脚约束才能进行下一步。

感谢小编分享!