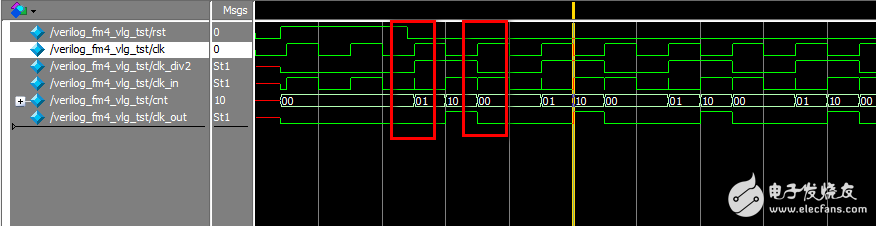

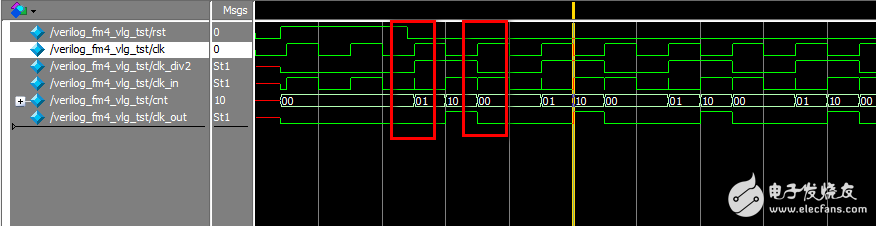

为什么这个程序仿真clk_in会出现这样的波形以及如何解决?

时间:10-02

整理:3721RD

点击:

程序源代码如下:

/******************************************************/

// DATA: 2015年7月20日14:25:09

// Project Name: verilog_fm4

// REVERSION: V1.0

// Description:分频计数实验----半整数分频实验

// Editor FPGA_Lover

/*******************************************************/

module verilog_fm4(

clk,rst,

clk_in,

clk_div2,

clk_out,

cnt

);

input clk;

input rst;

output clk_in;

output clk_div2;

output clk_out;

output [1:0] cnt;

wire clk_in;

reg clk_div2;

reg clk_out;

/******************************************************************/

// 系统时钟二分频模块

//

//

/******************************************************************/

always @(posedge clk or posedge rst) begin

if(rst) clk_div2 <= 1'b0;

else clk_div2 = ~clk_div2;

end

/*******************************************************************/

// 模3计数时钟

//

//

/*******************************************************************/

assign clk_in = clk ^ clk_div2;

/*******************************************************************/

// 模3计数模块

//

//

/*******************************************************************/

reg [1:0] cnt;

always @(posedge clk_in or posedge rst) begin

if(rst) begin

cnt <= 2'd0;

clk_out <= 1'b0;

end

else if(cnt == 2'd1) begin

clk_out <= ~clk_out;

cnt <= cnt + 1'b1;

end

else if (cnt == 2'd2) begin

clk_out <= ~ clk_out;

cnt <= 1'b0;

end

else

cnt <= cnt + 1'b1;

end

endmodule

/******************************************************/

// DATA: 2015年7月20日14:25:09

// Project Name: verilog_fm4

// REVERSION: V1.0

// Description:分频计数实验----半整数分频实验

// Editor FPGA_Lover

/*******************************************************/

module verilog_fm4(

clk,rst,

clk_in,

clk_div2,

clk_out,

cnt

);

input clk;

input rst;

output clk_in;

output clk_div2;

output clk_out;

output [1:0] cnt;

wire clk_in;

reg clk_div2;

reg clk_out;

/******************************************************************/

// 系统时钟二分频模块

//

//

/******************************************************************/

always @(posedge clk or posedge rst) begin

if(rst) clk_div2 <= 1'b0;

else clk_div2 = ~clk_div2;

end

/*******************************************************************/

// 模3计数时钟

//

//

/*******************************************************************/

assign clk_in = clk ^ clk_div2;

/*******************************************************************/

// 模3计数模块

//

//

/*******************************************************************/

reg [1:0] cnt;

always @(posedge clk_in or posedge rst) begin

if(rst) begin

cnt <= 2'd0;

clk_out <= 1'b0;

end

else if(cnt == 2'd1) begin

clk_out <= ~clk_out;

cnt <= cnt + 1'b1;

end

else if (cnt == 2'd2) begin

clk_out <= ~ clk_out;

cnt <= 1'b0;

end

else

cnt <= cnt + 1'b1;

end

endmodule

程序要实现的功能是实现2.5分频

我学的是VHDL,你能说说你的CNT是干什么用的?

分频的时候,计数用的!

clk_in = clk ^ clk_div2,用了异或,clk和clk_div2的沿没有对齐,clk_div2为clk的分频,是不是引入了延时导致这两个时钟的沿没有对齐

always @(posedge clk or posedge rst) begin

clk_in <= clk ^ clk_div2;

end

这样打一拍就行了