请教关于功能仿真出现的问题

时间:10-02

整理:3721RD

点击:

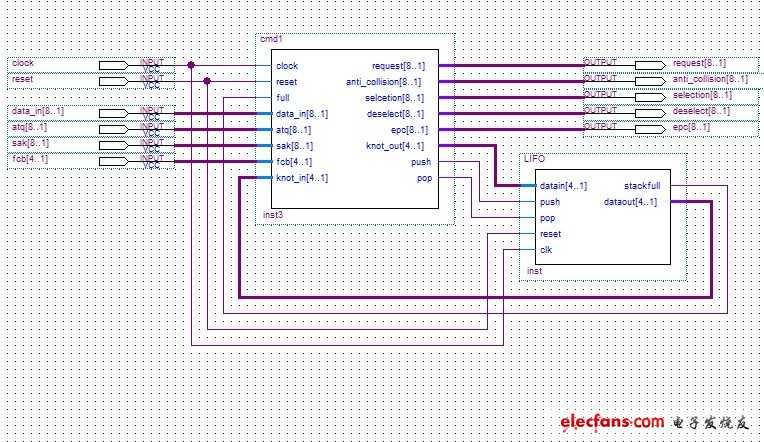

图中的两个模块单独进行功能仿真调试的时候都没有问题,各输入输出都正常,但是连接到一起之后,push、pop、knot_in、full都没有了,导致无法读取后先出堆栈LIFO中的数据,求高手指导一下,这个是什么原因,应该怎么解决?

仿真的时候没有错误,只有警告类似于:

Warning: Can't find node "cmd1:inst3|full" for functional simulation. Ignored vector source file node.

......

总连接图

应该是你没设置好。要先把该原理图设成顶层文件,编译后将各个输入输出管脚添加到仿真波形,再仿真。单独模块仿真没问题的话,总的一般也没问题,我一般不再仿真。

在时序仿真文件中找不到对应的节点“full”。是不是内部程序没有连接到这个输出管脚?

不过还是最好是结合代码分析,只是一个警告不足以查找问题所在!