verilog代码quartus II下时序仿真出现两个时钟延时,请问怎么...

时间:10-02

整理:3721RD

点击:

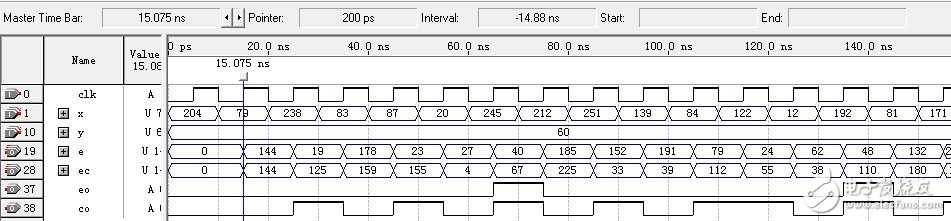

我用verilog编了一个减法代码,但是在FPGA下的时序仿真却出现了时钟延时,请问我的代码有什么问题吗?(代码的内容:输入x和y,e=y-x,eo表示正负,ec是后一个e与前一个e的误差,co表示正负)

代码如下:

module jianfa (x, y, clk, e, ec, eo, co);

input[7:0] x;

input[7:0] y;

input clk;

output[7:0] e;

reg[7:0] e;

output[7:0] ec;

reg[7:0] ec;

output eo;

reg eo;

output co;

reg co;

reg[7:0] a;

reg[7:0] b;

reg m;

reg n;

always @( posedge clk)

begin

if (y >= x)

begin

a = b)

begin

ec = b)

begin

ec <= a - b ;

co <= 1'b1 ;

end

else if (a < b)

begin

ec <= b - a ;

co <= 1'b0 ;

end

end

e <= a ;

end

endmodule

仿真结果如下:

代码没有问题,同步逻辑电路就是靠时钟工作的,第一个上升沿取数据,第二个时钟的上升沿才会输出数据。所以仿真是没有问题的。