板级电源完整性探讨:去耦电容对策

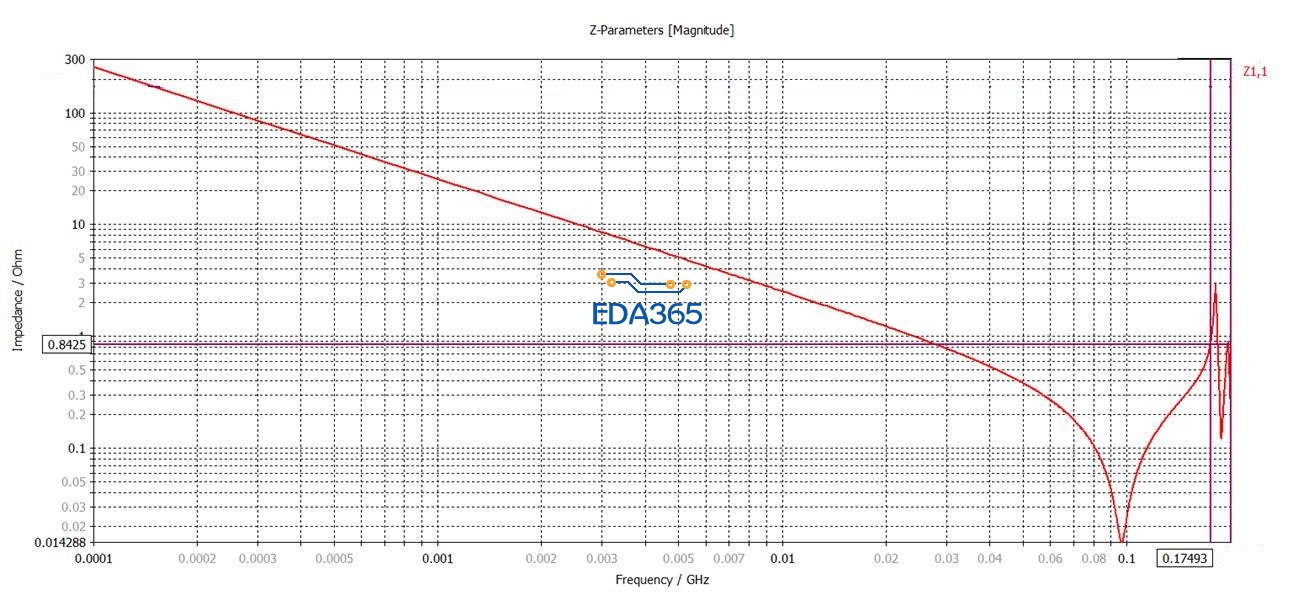

这是我一个裸板的(没有任何部件)仿真结果。

假设目标阻抗为:0.84欧姆

按照图上显示的第一反共振与目标阻抗相交的频率为0.17493。能设为去耦电容有效上限频率吗?

各位大侠会如何着手降低阻抗值呢?

另外请问如何模拟电源(VRM)的参数?一个电感串联一个电阻行得通吗?

真心求教! 感谢!

VRM确实很重要,但是那主要是针对30MHz以下的

30MHz以上时,VRM的影响不大,当然前提是你不要用过于夸张的ESR和ESL。我的做法通常是把VRM的等效阻抗设置为0.001ohm以上,0.1ohm以下,具体设为多少,依照你的电压源的寄生参数决定,(不必做得过于精确,因为即使你用阻抗仪去测也会有误差,而且VRM设为0.1ohm以下的PDN在0-30MHz的变化已经不大了),这样你就可以看到30MHz以下的PDN。

至于这个公式,他其实没有直接告诉你,这个电容是理论上直接贴在IC pin脚上的,然而实际上,这是不现实的,所以理论公式只能帮助你得到一个方向,实际上贴片元件到IC pin的电源路径,地路径带来的寄生参数影响都要考虑进计算中,所以这部分必须依靠仿真帮助我们计算。

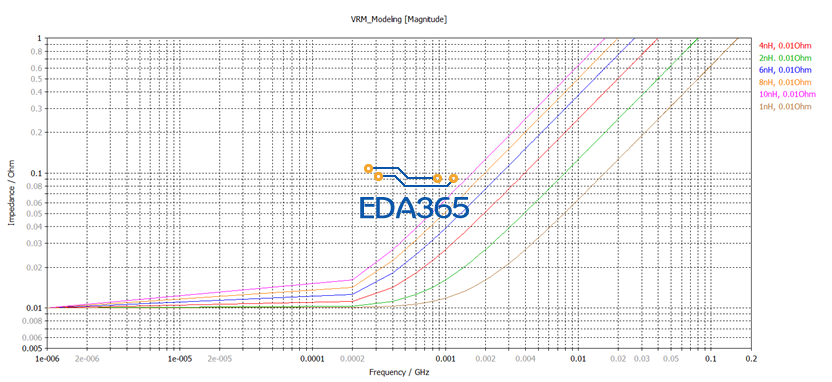

可以的,可先用0.1 Ohm串聯一個電感,電感值假定是數百nH~xuH,實際R、L值依你的VRM而定。

另外水平的刻度調整一下,讓觀察的範圍左xMHz ~ 百MHz 極大化。

感谢honejing的指导。

我尝试了sweep几个不同电感值,固定R为0.01欧姆。水平刻度最大设为200MHz。所仿真到的最大R值在200MHz时不超过14欧姆。

在这几个电感值当中,请问您觉得哪一个比较合理,比较接近最近的高性能VRM?

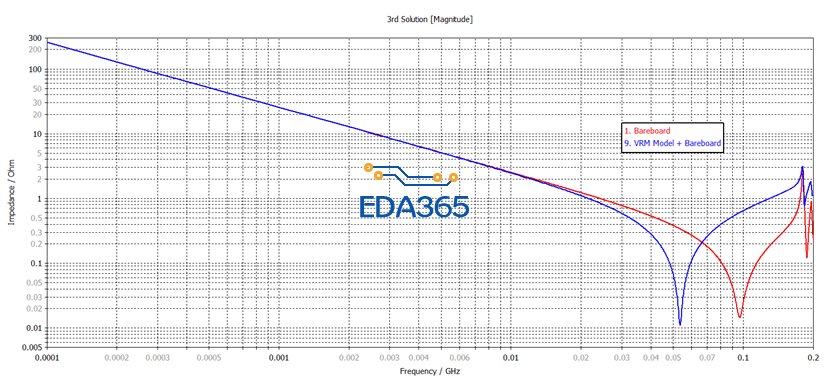

接着,我尝试把1nH+0.01欧姆的VRM Model结合Bareboard来进行仿真,Bareboard的0Hz-100KHz频段的capacitive没法压下来。

尝试使用更大的电感值1uH也只不过是把plane capacitive的共振点往左移而已。

有什么更好的方法来为VRM建模呢?

还有一点,只导入VRM model而不导入至少1个电解电容(数uF),是没办法看到低频段被压低阻抗的现象。这样的仿真可信吗?

再来一点, 倘若把VRM的串联电感值设得过高(10nH),按照Bogatin的公式,n>2PI x fmax x ESL / Ztarget, 得加上几十个电容才能把整体阻抗拉小。10-20个电容根本起不了什么作用。

VRM电感是和去耦电容的寄生电感串联的。

感觉能否设计一个精度高的PDN,VRM建模起着决定性的作用。各位看法如何?

来学习知识

不错,,,用的上

哈哈哈。学习一下

学习

不知道

学习