SI-listAllegro Sigrity OptimizePI Training(二)去耦电容仿真设置

SI-list【中国】Allegro Sigrity OptimizePI Training(二)去耦电容仿真设置

原创 2016-07-27 李黎明 shark4685

本文大纲

1. 去耦电容仿真设置(一)

2. 去耦电容仿真设置(二)

3. 去耦电容仿真设置(三)

4.仿真优化结果查看

关于OptimizePI

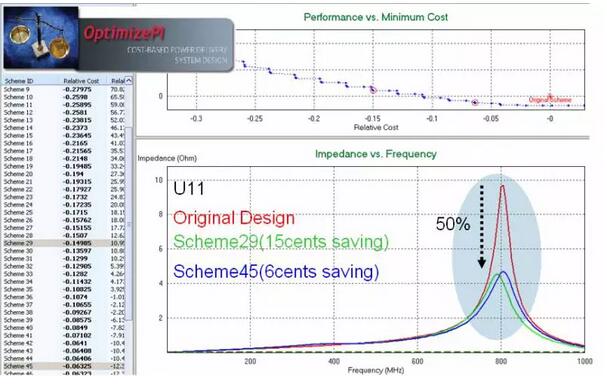

去耦电容的优化需要综合考虑PDN的性能和成本因素,在目前的PCB或封装设计中,往往存在PDN电源噪声(包括低频和高频)超标、性能不满足设计、成本较高等问题。随着设计变得越来越复杂,电容的位置和容值选择往往大大超出设计人员的经验。

OptimizePI提供业界第一个能够综合考虑电源PDN性能和成本的解决方案。OptimizePI使用专利的电磁分析和优化算法,可以快速、准确地进行电源分析,自动排列组合去耦电容的容值和位置,提供兼顾性能和成本的电容优化方案,根据优化的不同目标,帮助设计人员在成本、空间、数量和性能之间做出权衡。OptimizePI提供交互式的优化结果后处理,方便用户直观地选择优化结果

去耦电容仿真设置(二)

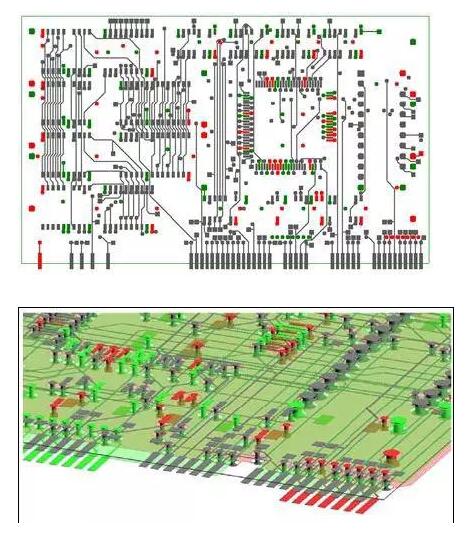

本模块用到的PCB案例:

1. 6层PCB设计,第2层是地平面、第5层是电源平面

2.1个电源网络:VCC(红色显示网络)

3.1个地网络:GND(绿色显示网络)

4.1个VRM、5个IC器件(阻抗观测点)、28个去耦电容

本模块中,我们将会用OptimizePI分析不同的电容滤波方案对几个IC器件的电源阻抗的影响,从OptimizePI推荐的方案中选择合适的方案优化PDN设计。

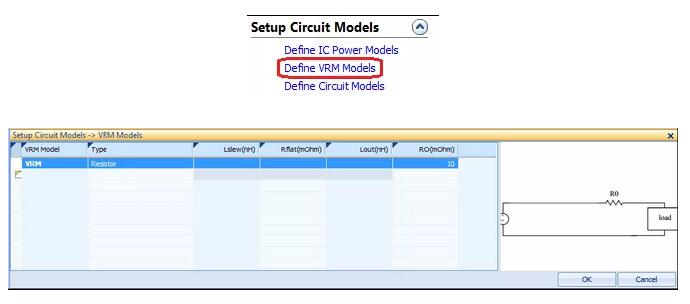

9. 在Workflow中选择“Define VRM Models”,添加VRM的模型,类型选择Resistor,阻值按默认的10 mohm,点击OK确认。

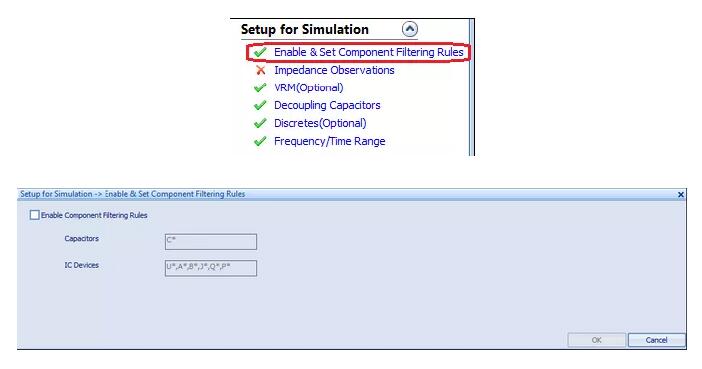

10. 在Workflow中选择“Enable & Set Component Filtering Rules”。在这一步可以通过匹配器件位号自动把相应的器件定义为阻抗观测点或者需要优化的电容。本案例中我们将手动设置阻抗观测点和电容,这里保留“Enable Component Filtering Rules”选项为不使能状态。

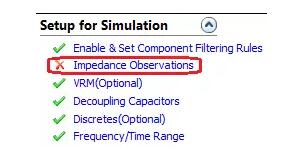

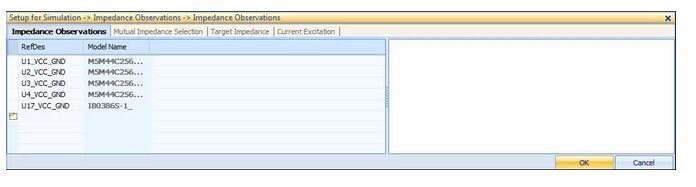

11. 在Workflow中选择“Impedance Observations”

在弹出的Circuit Generation Wizard页面,选择“Create By Nets”,点击Next

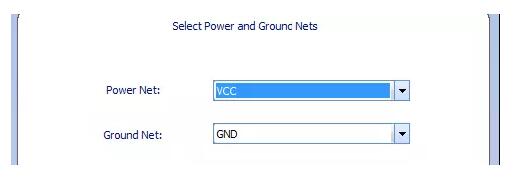

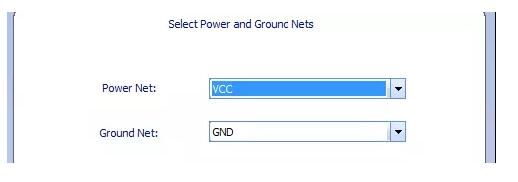

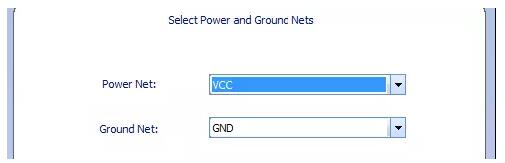

在下一页,设置Power Net为“VCC”,Ground Net为“GND”,点击Next。

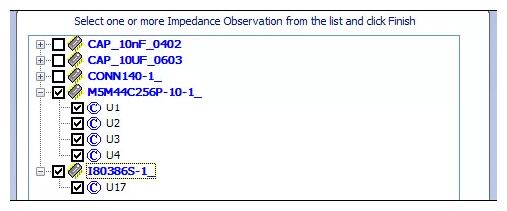

在下一页,勾选U1-U4、U17等器件,点击Next。

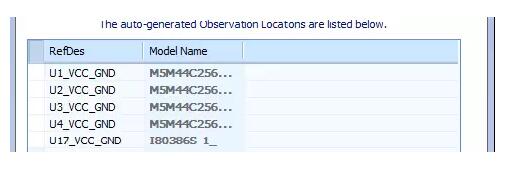

在下一页,可以设置阻抗观测点的器件模型,本例不进行修改,点击Finish。

在主界面的Setup for Simulation->Impedance Observations页面,点击OK确认。

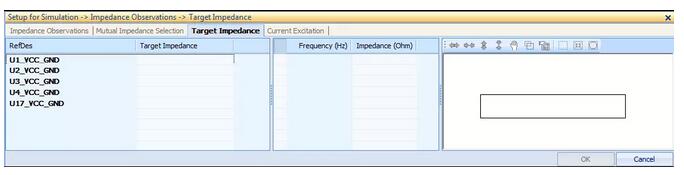

在Target Impedance可以设置每个阻抗观测点的目标阻抗。OptimizePI优化得到的阻抗曲线都将会在目标阻抗以下。本案例将采用Threshold Impedance仿真进行优化,这里不需要Target Impedance。

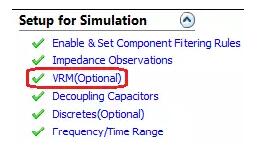

12. 在Workflow中选择“VRM(Optional)”

在弹出的Circuit Generation Wizard页面,选择“Create By Nets”,点击Next。

在下一页,设置Power Net为“VCC”,Ground Net为“GND”,点击Next。

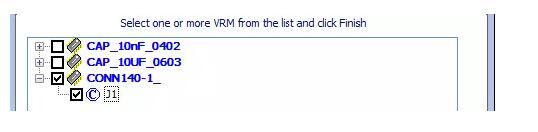

在下一页,勾选J1器件,点击Next。

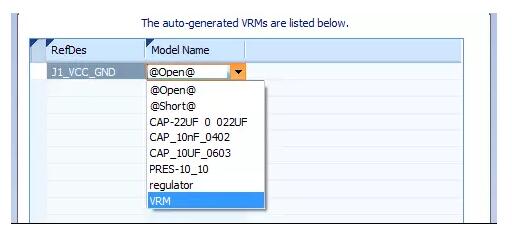

在下一页,检查设置为VRM的器件,设置J1_VCC_GND的模型为“VRM”,点击Finish。

在主界面的Setup for Simulation->VRM(Optional)页面,点击OK确认。

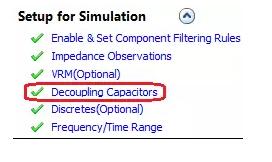

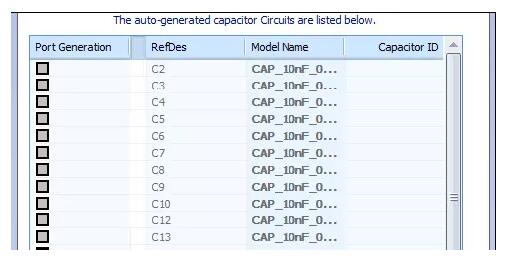

13. 在Workflow中选择“Decoupling Capacitors”,

在弹出的Circuit Generation Wizard页面,选择“Create By Nets”,点击Next。

在下一页,设置Power Net为“VCC”,Ground Net为“GND”,点击Next。

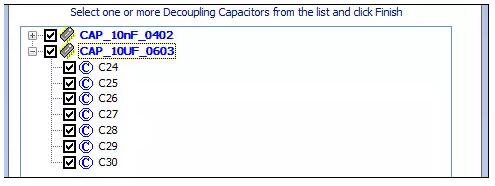

在下一页,勾选CAP_10nF_0402和CAP_10UF_0603的所有器件,点击Next。

在下一页,检查需要优化的电容,点击Finish。

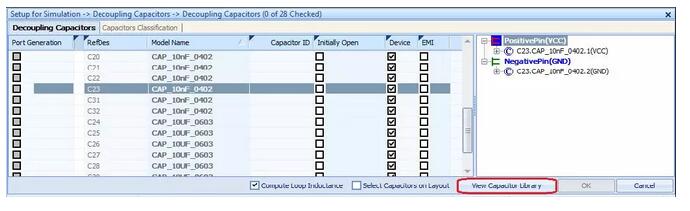

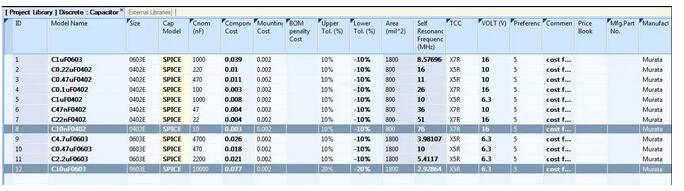

14. 在主界面的Setup for Simulation->Decoupling Capacitors页面,点击“View Capacitor Library”按键,打开Analysis Model Manager窗口。

在电容库中查找到0402封装10nF电容和0603封装10UF电容的ID分别为8和12。

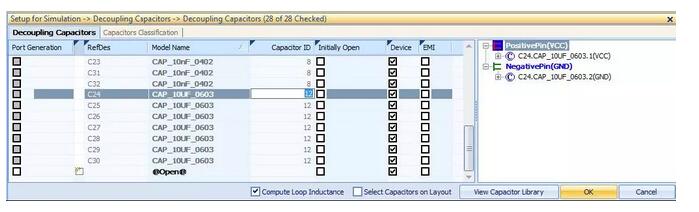

在主界面的Setup for Simulation->Decoupling Capacitors页面,将查找到的ID填入CAP_10nF_0402和CAP_10UF_0603电容的Capacitor ID列。然后点击OK确认。

-----本节完,共四章----

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

PUSH

謝謝分享

謝謝分享~~

謝謝分享

谢谢分享!

感谢小编分享

:lol:lol:lol