PCB金手指 疊構設計 阻抗匹配設計

时间:10-02

整理:3721RD

点击:

目前設計子板PCB使用的是四層板- 上到下高速S-G-V-S方式 , 訊號為10Gbps

請問各位設計金手指部分中間G-V都是裸空的嗎? 對於差分阻抗匹配來講的確需要將金手指下面參考層加厚

來增加阻抗匹配值

1.根據高速訊號線回流路徑觀點,下方已經沒有參考層提供回流路徑(第四層雖然會有pad,但是那並非是VCC

或GND pad),而差分訊號已經在子板金手指部分經由socket流入母版PCB,這時候在socket中的回流路徑會走

哪一個接點? 主要是在正負差分訊號隔壁路的訊號線上嗎? 還是主要是金手指上GND的腳位? 我相信應該會

有一定相差比例關係,但不知是以哪一個為主?

2.若是我增加第三層的GND參考面在金手指高速訊號線正下方(計算後阻抗匹配值:85R),雖然阻抗匹配值會

比完全沒有參考面(95R)還來的糟一些請問就算阻抗匹配差一些,是否有無讓訊號反而更好的理論或實驗依據?

感謝各位大師求解

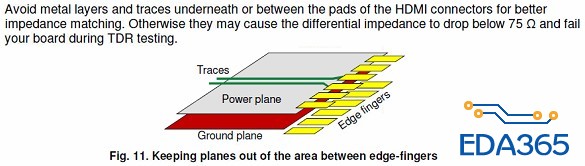

附件圖片跟我設計的GND 與VCC剛好擺相反,作一簡單疊構圖示範例參考

这个学习一下

我在搞这个板子的时候,直接把金手指下面的全部镂空,或者金手指下面的那块中间贰层水铺。因为这个位置本身就是阻抗不匹配的地方。

我在搞这个板子的时候,直接把金手指下面的全部镂空,或者金手指下面的那块中间贰层水铺。因为这个位置本身就是阻抗不匹配的地方。

学习一下,没有大神回复啊

路过学习学习啊!

问问题条理不清晰,加上下面几个瞎捣鼓。偶凌乱了。

1.金手指下面全部掏空的原因

金手指的部分因为要拔插,在制作工艺上是需要额外电镀的,这个工艺会增加板厚,但在工艺制程上为了控制整板厚度一致,所用将金手指下面的平面层挖空。

2.掏空带来的问题

线的阻抗没办法控制了。差分互相参考,并且差分间都有GND,可以用pwm模式控制阻抗,,单端信号如果是低速的还马马虎虎,如果有单端时钟,一般也是在其左右都是GND,通过pwm模式来控制阻抗。

所以不用担心没有办法走高速信号。PCI3.0 X1,X4,X8,X16.8G的传输速率杠杠的,没问题。

掏空还有个好处:就是可以阻断外部的单端噪声耦合进入板卡,差分噪声直接减掉了。无所谓。

何为PWM模式控制阻抗?

路过学习学习啊!

不知道怎么入手画内存条!

掏空是对的,这里高速信号的回路在两侧的地焊盘上

何为PWM模式控制阻抗?

金手指位置的高速线焊盘位置内层是需要掏空的,这个在协议上也可以查到告诉信号的阻抗和回路靠两侧地焊盘来满足。如果速率到25g,手指焊盘的宽度就要变为0.54mm,这个协议上也有指出。

你好

能否不吝於指導是哪一份文件上指出25G上的pad需要重新定義設計

感謝