SI-listAllegro Sigrity PowerSI Training (一)提取模式仿真设置

SI-list【中国】Allegro Sigrity PowerSI Training (一)提取模式仿真设置

原创 2016-03-10 李黎明 shark4685

本文大纲

1. 提取模式仿真设置

2. 仿真选项设置

3. 仿真结果查看

4.S参数后处理

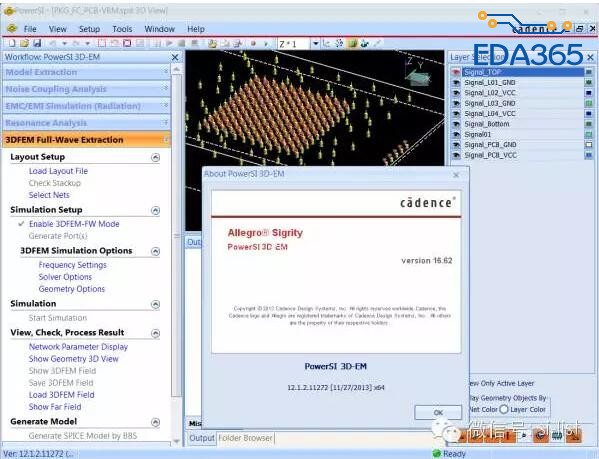

PowerSI-高效、精准的频域电源完整性及信号完整性分析工具

PowerSI利用独有的电磁混合仿真引擎能够高效准确地为设计人员提取信号或电源平面的网络参数(S/Y/Z),涵盖频段从DC至Ghz,并进行空间模式下的噪声分布及本征结构的谐振模式分析,在设计初期发现和定位设计中的各种风险及问题,给出准确直观的优化方向。最新的全波电磁分析引擎能够处理各种复杂的PCB/封装结构,在相同的仿真精度下,仿真速度比同类软件快。

提取模式仿真设置

1. 开始菜单->Cadence->Sigrity 2015->Sigrity Suite Manager。

2. 选择PowerSI,在右边窗口选择可用的license双击启动PowerSI。

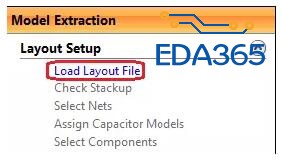

3. 在Model Extraction的workflow中选择“Load Layout File”。打开“D:\Training\Sigrity_PowerSI\Lab\Module1\tutorial_PCB1.SPD”。

4. 在workflow中选择“Load a New/Different Layout”,在弹出的对话框选择“Load an existing layout”,打开“D:\Training\Sigrity_PowerDC\Lab\Module1\tutorial_PCB1.spd”。

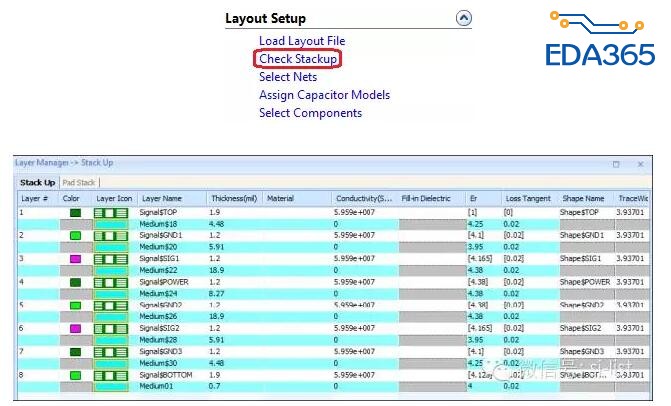

5. 在workflow中选择“Check Stackup”,打开Stack Up窗口。检查并设置金属层、介质层的厚度和材料参数。设置完成后点击OK按钮回到主界面。

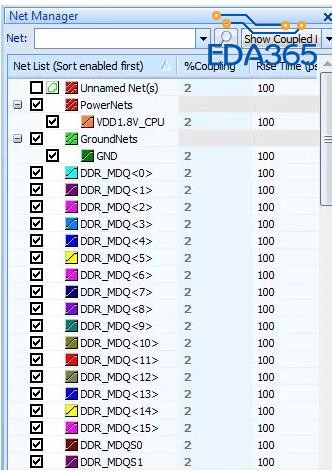

6. 在workflow中选择“Set up P/G Nets”->“Skip setup P/G nets”。在Net Manager页面,如下图所示,在PowerNets勾选“VDD1.8V_CPU”, 在GroundNets勾选“GND”,在SignalNets中勾选“DDR_MDQ<0-15>”和“DDR_MDQ0”、“DDR_MDQ1”。

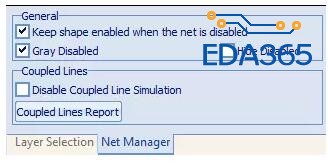

注意Show Coupled Line模式下,默认线间耦合的阈值设置的是2%-100ps,即近端串扰耦合系数超过2%的线间耦合才会进行建模,2%以下的线间耦合会忽略掉。100ps的上升沿时间用于计算耦合长度是否已经使近端串扰饱和。点击Net Manager页面下方Coupled Lines Report可以查看走线间耦合情况。

Net Manager页面下方的options中勾选“Keep shape enabled when the net is disabled”,在仿真中把其它没有使能的网络的shape都加入计算。

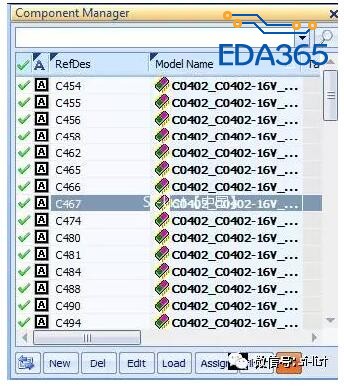

7. 在workflow中选择“Select Components”,打开Component Manager页面。

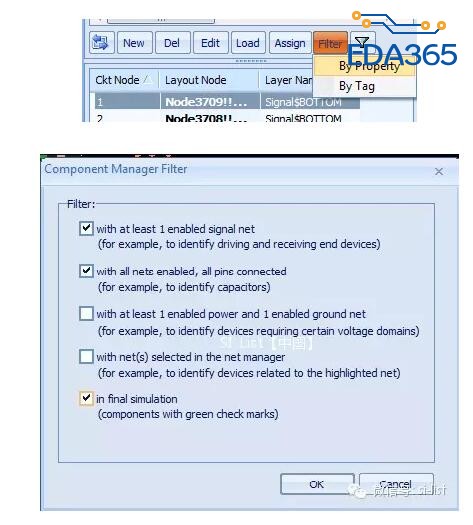

在Component Manager页面,点击Filter->By Property,在Component Manager Filter窗口勾选“with at least 1 enabled signal net”、“with all nets enabled, all pins connected”和“in final simulation”这几个选项。点击OK执行过滤。

可以看到,过滤后只会显示和仿真相关的器件,可以方便地检查和设置器件的电气模型。

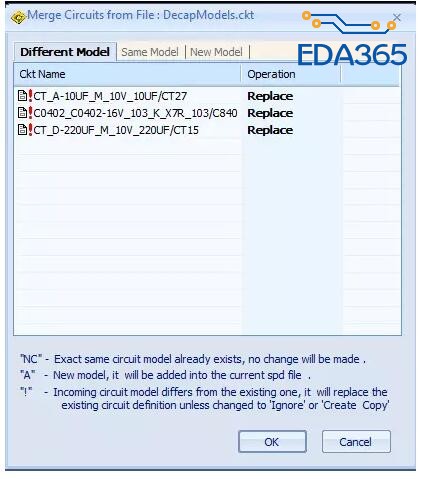

8. 在Component Manager页面,点击Load按键,导入“D:\Training\Sigrity_PowerSI\Lab\Module1\DecapModels.ckt”文件。在Merge Circuit from File窗口,点击OK按键,更新电容模型定义。

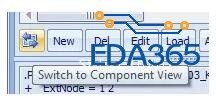

点击![]()

注:关于模型定义设置,可以参考Sigrity Layout Edit和Analysis Model Manager的相关内容。

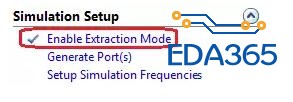

9. 在workflow中选择“Enable Extraction Mode”,确保前面有符号。

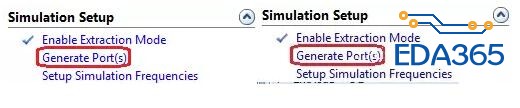

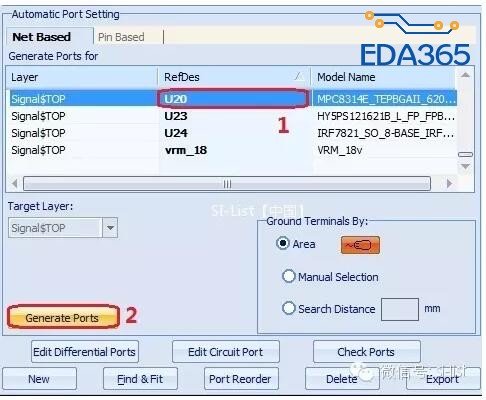

10. 在workflow中选择“Generate Port(s)”。

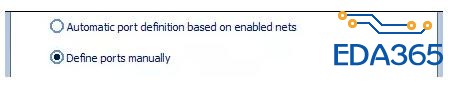

在弹出的Wizard窗口选择Define ports manually,点击Finish,打开Port窗口

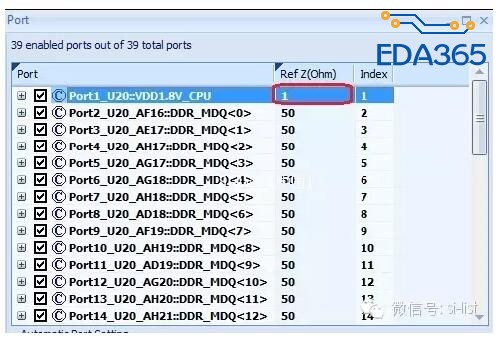

11. 在Port窗口选择“U20”器件,然后点击“Generate Ports”,PowerSI会根据Net Manager页面使能的网络,自动在U20器件相关管脚上生成Port。用同样的方法,在U23和vrm_18器件上生成Port。

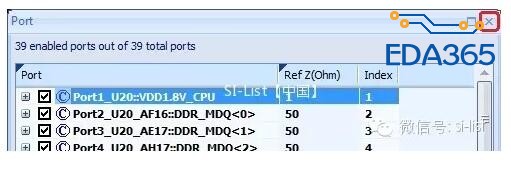

把VDD1.8V电源的几个Port的Ref Z改成1Ohm。

点击右上角的![]()

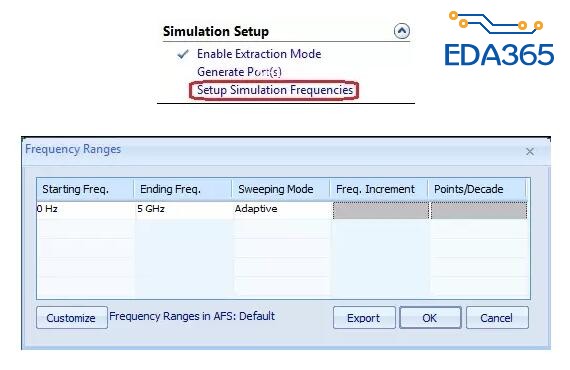

12. 在workflow中选择“Generate Port(s)”。设置仿真频率为0-5GHz,扫频方式为Adaptive。

-----本节完,未完待续----

本教程案例已在群公众号共享,到公众号点击案例下载加入学习,,,,,

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

好文,支持一个,不过这款软件个人用户光是安装就费劲~~

这个必须顶,这样实战性的文章最好。

现在下载不了案例了啊

這文章內容淺顯易懂,非常實用啊

感谢小编分享!

现在下载不了案例了啊现在下载不了案例了啊现在下载不了案例了啊现在下载不了案例了啊