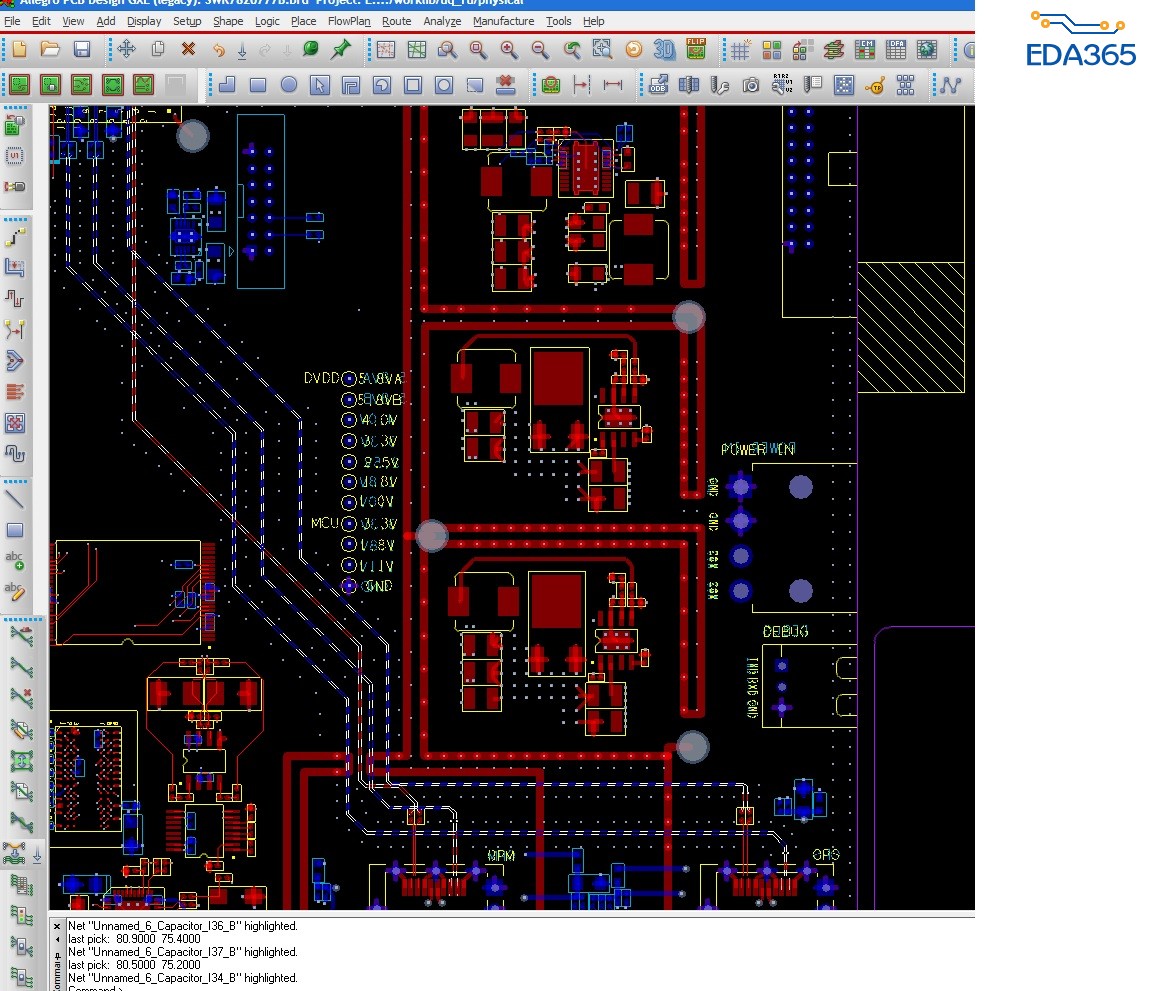

关于10G走线问题请教大神。谢谢。

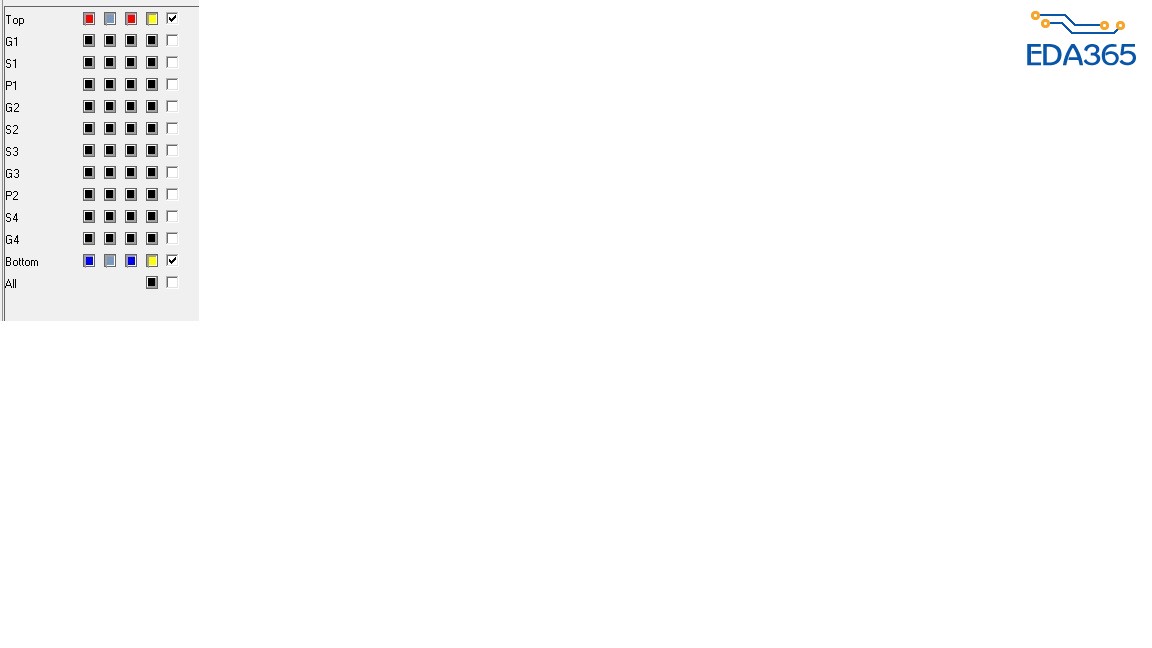

虽然你说的是10G的信号,但是10G的信号有非常多的协议,不同的协议对设计有不同的要求,要是是10Gbase KR的话,这种长度也不算什么?虽然,从某种意义上来讲,减少线长确实可以带来不一样的performance,但是不一定就是好的;板材方面的选择,与上一个问题是一样的,要先了解是什么样的协议,当然,也可以考虑使用性能较好的材料,性能好的材料不仅仅体现在损耗上、还有可能体现在稳定性上、或者是铜箔和玻布等等,可以考虑使用M4/TU872HF,但是不是推荐你一定使用;第三点是非常有必要的,特别是在换到不同的参考层的布线层;层叠的设计也没有什么太大的问题,只要不要把高速信号布在S2和S3;当然,最好也不要布在S1。有问题再说

谢谢,10G信号是SFP+的

现在的问题是现在的板子挑光模块,一些差一点的光模块基本需要厂家重新调参数值才能使用;现在希望实现的是至少得保证各种厂家那边全部关掉预加重,由我们这边FPGA来实现预加重,保证板子的一致性,防止出现现在就算我们FPGA做了预加重还是要挑厂家的状况。

那确实就不能太长,如果像你现在的这种长度,真有可能需要好点的材料,或者你的设计要进行仿真优化设计

首先说明你产品的裕量不是很够,另外,也有可能模块差的不要不要的

可以仿真s参数看看,不同材质相差多少

FR4也有low dk low df的材质,不会比普通FR4贵太多,考虑下。

过孔阻抗一致性的问题会不会严重的影响到丢包呢,会,但是不像你这样认模块来的,应该是所有模块都有问题,所以我觉得过孔方面的优化优先级可以放后一点。

预/去加重是个好办法,按照规格书来仿真调整最佳的tap级别试试。

换板材,Df在0.005左右的,再又做背钻,即可。

这个长度的走线对于10G信号来说,不是特别长。个人建议还是不要去改板材和叠层,而是通过设置去加重和均衡的方式,去调整一个比较好的均衡和去加重值来尽量覆盖比较广的光模块。应该可以找到一个比较好的值,还有就是建议尽量通过去加重来实现。

这个长度的走线对于10G信号来说,不是特别长。个人建议还是不要去改板材和叠层,而是通过设置去加重和均衡的方式,去调整一个比较好的均衡和去加重值来尽量覆盖比较广的光模块。应该可以找到一个比较好的值,还有就是建议尽量通过去加重来实现。

感谢分享,我也正要设计一款此类型的。能否给点参与的。谢谢。

好深入的見解和建議! 謝謝!

最简单的方法 增加差分对线宽 O(∩_∩)O哈哈~你不走个8,mil以上 基本不行