如何理解串扰

串扰是令人讨厌的。串扰这个问题近年来随着信号速率的增加,越来越突出。而且,串扰这个问题一般都显得比较“高大上”。高端,因为真正搞明白串扰的人并不多;大气,因为对于串扰问题能谈得头头是道的,一定有大师之气象;上档次,因为因为串扰不太容易定量的测量,动不动就要和“仿真”的方法论联系起来。

“串扰是空间上的串扰,因此只和电磁场强度相关。电磁场强度以导线为圆心,向外层层减弱。去破坏这个圆的完整性,就是去减少串扰。” 这次讨论中朱永辉君给出了这个结论很是一语中的。阅读过之前微信群讨论会的朋友已经感受到朱永辉君的大师形象了。在硬件智库微信对框中回复数字20150331,您就可以读到朱大师的经典原创文章《高速数字总线时序分析及计算方法》。

------------------------------------------------------------------------------------------

讨论日期:2015-08-04

黎坚 17:05

为什么减少信号路径特性阻抗会减少串扰。这是信息完整性分析一书中的原文,我不理解所以想找个高人解答下。

wenming 17:13

@黎坚 不是减少阻抗,是匹配特性阻抗吧。和串扰的联系,我也需要听听专家的讲解,我只知道阻抗不匹配和信号损耗衰减有很大关系

小蒋 17:22

阻抗不匹配就会引起反射,如果存在串扰,也同样会在阻抗不连续点被反射,如果反射叠加,就会使串扰更大

朱永辉 17:25

我们通常讲的串扰是空间上的串扰,因此只和电磁场强度相关。电磁场强度以导线为圆心,向外层层减弱。去破坏这个圆的完整性,就是去减少串扰。

小蒋 17:30

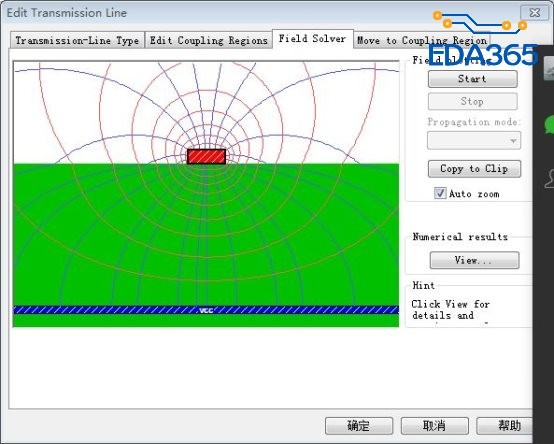

这是刚刚仿真得到的串扰结果。

薛定谔的猫 17:31

我们走的是微带线或者带状线。模型不是同心圆了。

小蒋 17:32

通过线宽改变了阻抗,串扰是不同,但是我觉得这是距离造成的。

杨安毅 17:33

针对降低阻抗的做法,我个人的理解是,阻抗降低,往往是通过增加线宽,线宽增加,抗干扰能力越强。

黎坚 17:33

谢谢专家解答。我也认同距离是减少串扰最直接的办法。

小蒋 17:36

@黎坚 一定可以,但是会有一个饱和度的问题。

朱永辉 17:38

距离是一个,同心圆也是一个。因为同心圆产生了3H原则。

小蒋 17:39

同心圆我倒是没有研究过。

黎坚 17:42

@老蒋,你们有仿过微带线与带状线串扰的差别吗?

小蒋 17:42

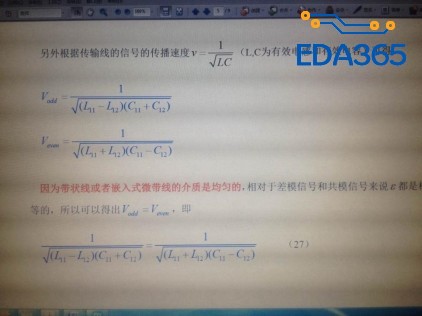

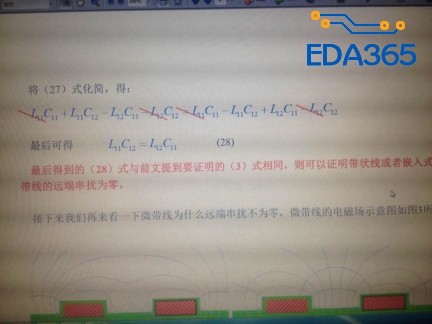

有。带状线小很多。因为由于介质均匀,所以起远端串扰趋近于0。理论说带状线的远端串扰为0。实际上不会完全对称和均匀,所以会有一部分。

黎坚 17:45

为什么?能详细解释下不。

小蒋 17:46

这个要推导呀。

周杰 英伟达 17:46

个人感觉仿真出来的xtlk比实际小。

小蒋 17:46

是的。

福大海矽-刘伟城 17:46

串扰针对源端,强度与空间上是呈一个类似橄榄球状辐射开。

小蒋 17:47

测试会大点。理论都是基于一点,实际却是整个系统。

杨安毅 17:52

实际测试主要要考虑PCB的介质不是均匀的。

黎坚 18:18

@老蒋,你是真正的专家。还烦解答下为什么均匀介质状态下远端串扰小。

小蒋 18:19

我就是是小工,朱总他们是专家!主要还是其模式转化,致使其正负相互抵消。

朱永辉 18:21

Crosstalk,串扰在Mentor Graphic的软件下,就是指两根线之间的互扰,和远端什么的没有关系。

福大海矽-刘伟城 18:24

这“远端”是指两线间的距离吗?距离越大,耦合度越弱,串扰就越小,这应该很容易理解,不用解释。

小蒋 18:26

不是两线的距离。是接收端相对于源端的位置。

朱永辉 18:29

这就是串扰的根源。导线周围的电磁场分布。3H原则就从这里得来。破坏了这个同心圆,就是破坏了串扰。3H原则这个H就是导线和参考平面的距离,而不是线间距。

福大海矽-刘伟城 18:33

两均匀间隔走线间,具有走线电容,在长线传输中,一定距离的走线,等同于一个个负载,负载会衰减信号强度,走到远端时,信号强度会变小,这可能是远端串扰小的原因吧。

H应该是参考平面与导线距离,谁小谁优先考虑其间的相互影响。

小蒋 18:38

福大海矽-刘伟城 18:41

我还是没能看懂。回家吃饭先,各位也别太迟啦!

增加线宽,以及减少走线与参考面的间距应该都可以降低串饶吧,一个是增大容量,降低感性耦合,从而减少串饶。另一个是减少磁场在空间的公布,从而也能减少串饶。

加大线间距的确可以降低串饶,但在布线空间有限的时候你能怎样加大线间距。传说中的2w及3w法则也有有前提的,如果这样可以解决问题,串饶也就没什么难点了。如果设计的好,少于2W/3W的线间距也可把串饶控制得很好。

被串扰的信号和串扰的信号是同相位还是反相位?