SI-listAllegro Sigrity PowerSI Training (四)S参数后处理

SI-list【中国】Allegro Sigrity PowerSI Training (四)S参数后处理

原创 2016-03-29 李黎明

本文大纲

1. 提取模式仿真设置

2. 仿真选项设置

3. 仿真结果查看

4.S参数后处理

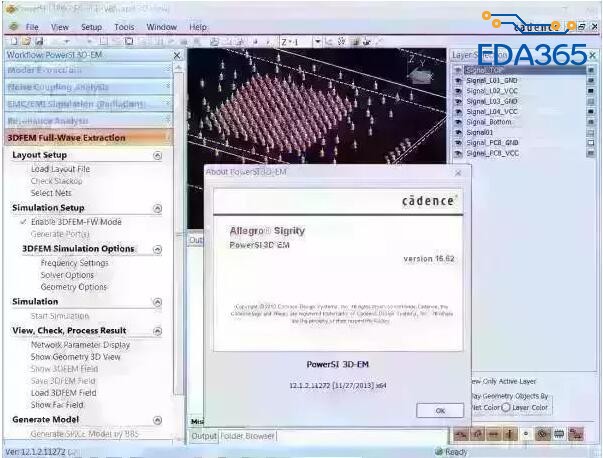

关于Power SIPowerSI-高效、精准的频域电源完整性及信号完整性分析工具

PowerSI利用独有的电磁混合仿真引擎能够高效准确地为设计人员提取信号或电源平面的网络参数(S/Y/Z),涵盖频段从DC至Ghz,并进行空间模式下的噪声分布及本征结构的谐振模式分析,在设计初期发现和定位设计中的各种风险及问题,给出准确直观的优化方向。最新的全波电磁分析引擎能够处理各种复杂的PCB/封装结构,在相同的仿真精度下,仿真速度比同类软件快。

S参数后处理

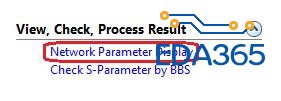

35. 在workflow中选择“Network Parameter Display”,打开一个新的S参数显示窗口

36. 在Network Parameters面板的空白区域,右键菜单选择Load,导入仿真工作目录下的tutorial_PCB1_Date_Time_ProcessID.bnp文件。

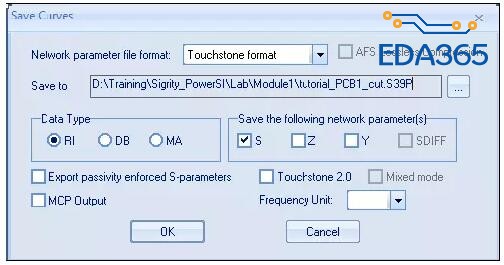

37. 在S1 S参数的Header行,右键菜单选择Save As,文件格式选择“Touchstone format”,把S参数另存为tutorial_PCB1.S39P。点击OK确认。

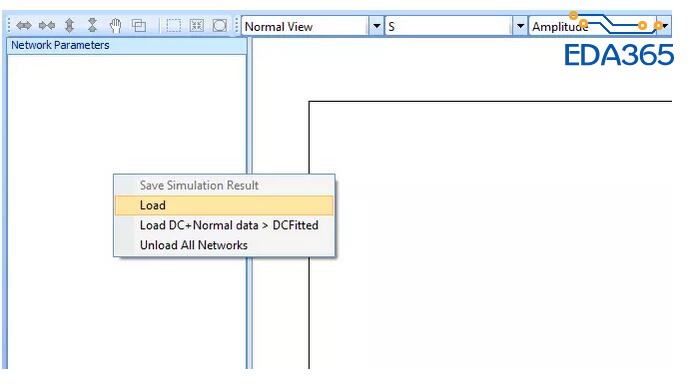

38. 在S1 S参数的Header行,右键菜单选择Matrix Operations->Redefine Differential Port。

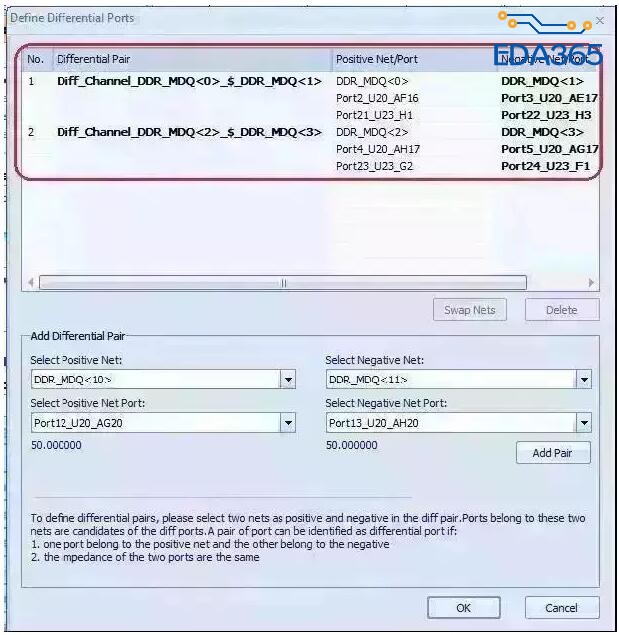

39. 在Define Differential Ports窗口,选择差分对网络以及对应的Port,点击Add Pair添加差分Port。

这里以MDQ<0-3>作为示例,如下设定MDQ0/MDQ1、MDQ2/MDQ3的Port作为差分Port。点击OK确认。

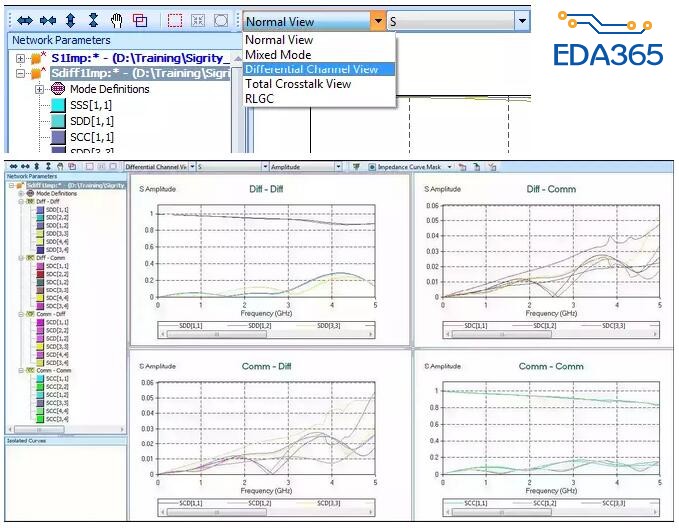

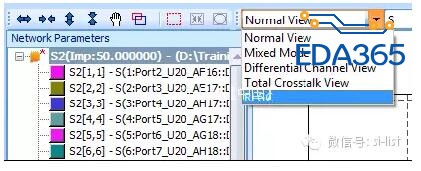

40. 切换到Differential Channel View

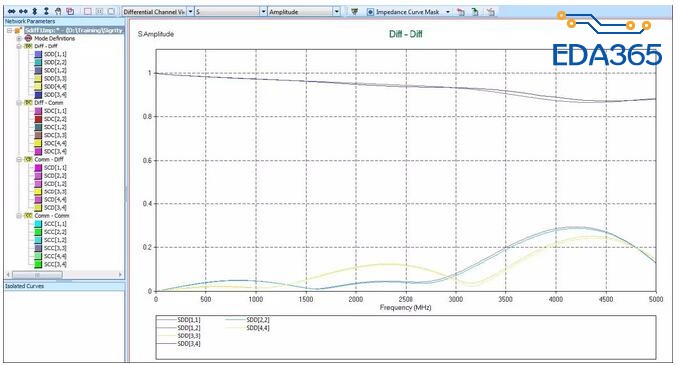

在Diff-Diff S参数显示区域,空白处双击,切换Diff-Diff窗口最大化。再次双击可以切换回上图SDD/SDC/SCD/SCC 4个窗口同时显示。

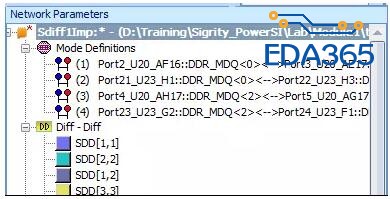

41. 展开Mode Definitions,可以看到差分Port定义情况

42. 切换回Normal View。

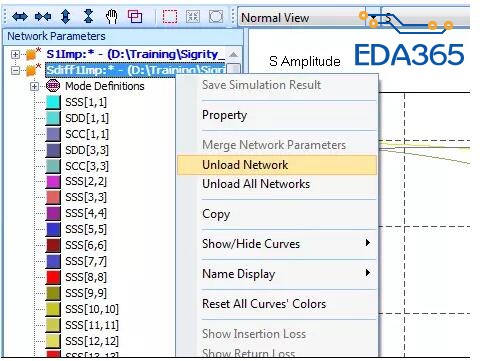

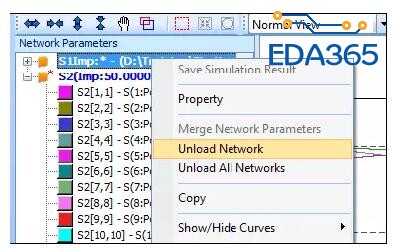

在Sdiff1 S参数Header行右键菜单选择Unload Network,在提示保存的窗口,选择不保存。

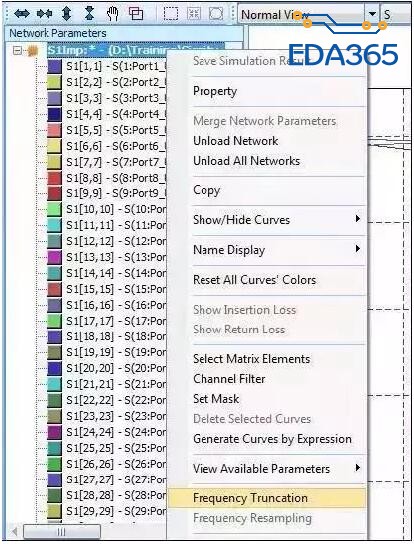

43. 重新导入tutorial_PCB1.S39P文件。在S1 S参数的Header行,右键菜单选择Matrix Operations->Frequency Truncation。

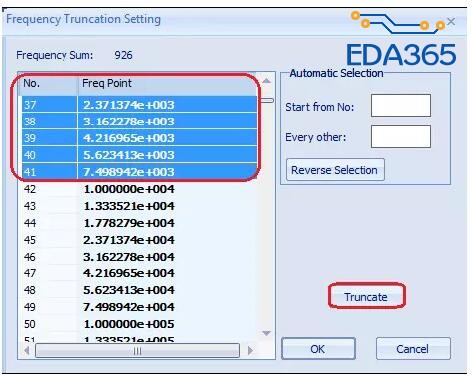

选中10KHz一下的频点,然后点击Truncate按键。点击OK确认。

把S参数另存为tutorial_PCB1_cut.S39P

44. 在Network Parameters面板的空白区域,右键菜单选择Load,导入仿真工作目录下的tutorial_PCB1_Date_Time_ProcessID_DC.bnp文件。把S参数另存为tutorial_PCB1_DC.S39P。

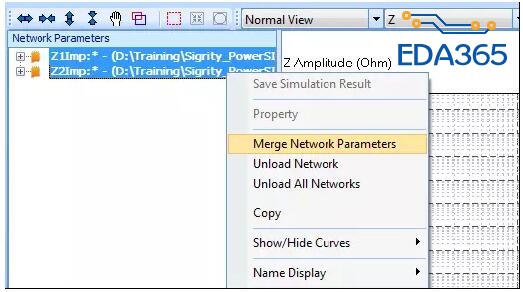

45. 同时选中tutorial_PCB1_cut.S39P和tutorial_PCB1_DC.S39P这两个S参数,右键菜单选择Merge Network Parameters。

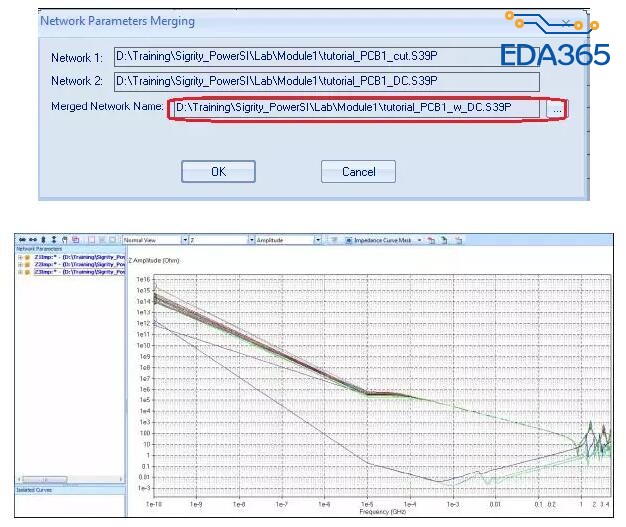

合并这两个S参数,合并后的文件保存为tutorial_PCB1_w_DC.S39P。点击OK确认。

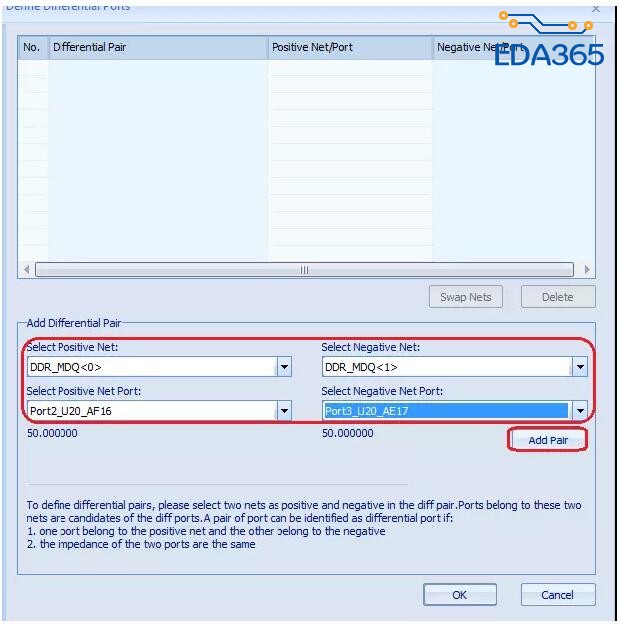

46. 在workflow中选择“Network Parameter Display”,打开一个新的S参数显示窗口。在Network Parameters面板的空白区域,右键菜单选择Load,导入tutorial_PCB1.S39P文件。

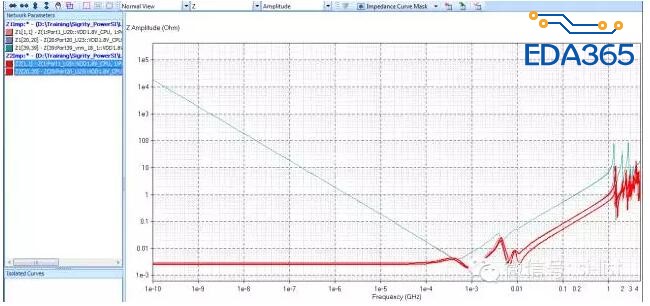

47. 用Channel Filter选择只看VDD1.8V_CPU的Return Loss。切换到Z参数显示。

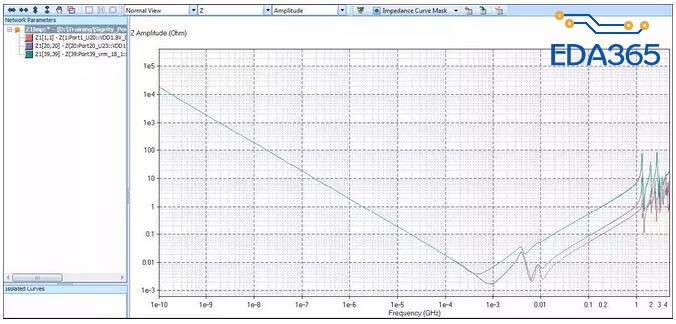

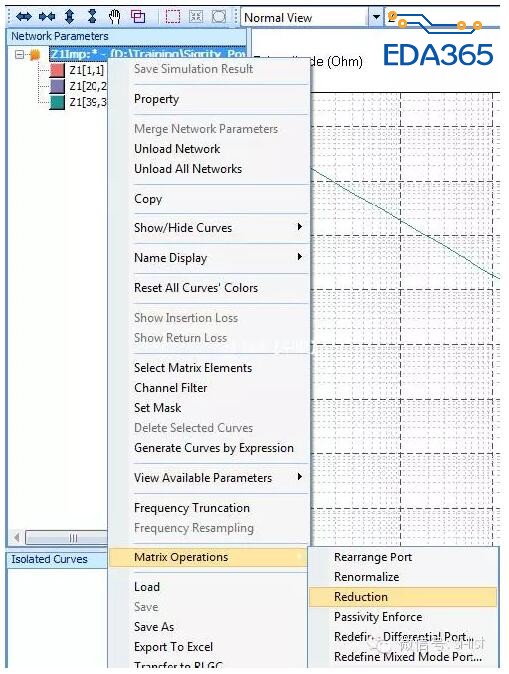

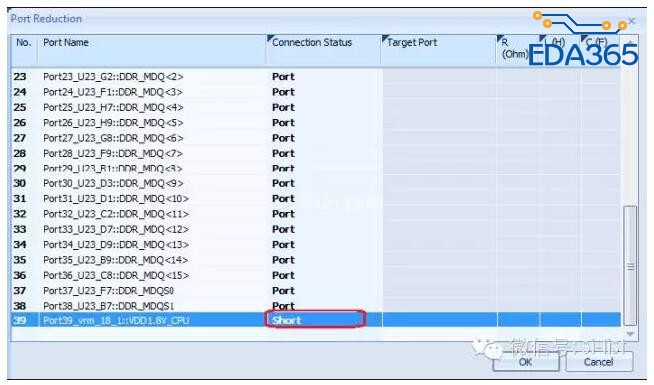

48. 在Z1 Z参数的Header行,右键菜单选择Matrix Operations->Reduction。

把Port39_vrm_18_1::VDD1.8V_CPU的Connection Status改成Short。点击OK确认。

查看在VRM短路情况下,其余两个电源Port的短路阻抗如下。

49. 在workflow中选择“Network Parameter Display”,打开一个新的S参数显示窗口。在Network Parameters面板的空白区域,右键菜单选择Load,导入tutorial_PCB1.S39P文件。

50. 用Matrix Operations->Reduction的方法,把VDD1.8V_CPU网络的3个Port,都改成short。点击OK确认。

51. 在S1 S参数的Header行,右键菜单选择Unload Network。

52. 在工具栏把Normal View切换成RLGC。

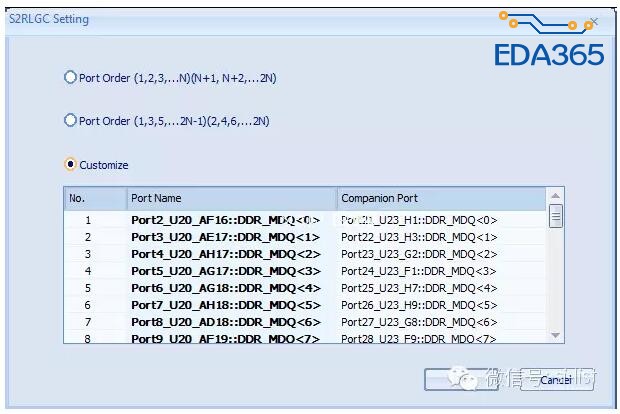

在S2RLGC窗口,选择Customize,设置每个Port对应的传输线另一端的Port。

查看S参数转换得到的RLGC参数、特征阻抗、传输延时等。

-----本文完,共四章----

本教程案例已在群公众号共享,到公众号点击案例下载加入学习,,,,,

关于SI-list【中国】微信群

本群专注于:高速链路设计,信号完整性,电源完整性仿真,测试,验证相关技术交流,经验分享,解疑答惑,如方便,可把单位,研究方向在群名称表示出,方便大家交流合作,如果消息太多设置为免打扰模式,不便的可退群。

注明加SI-list【中国】微信群.

操作了一遍,还是有点蒙圈。

软件不熟悉,不明白一些步骤,为什么这么操作。

学习了,顶