关于DDR时钟波形

时间:10-02

整理:3721RD

点击:

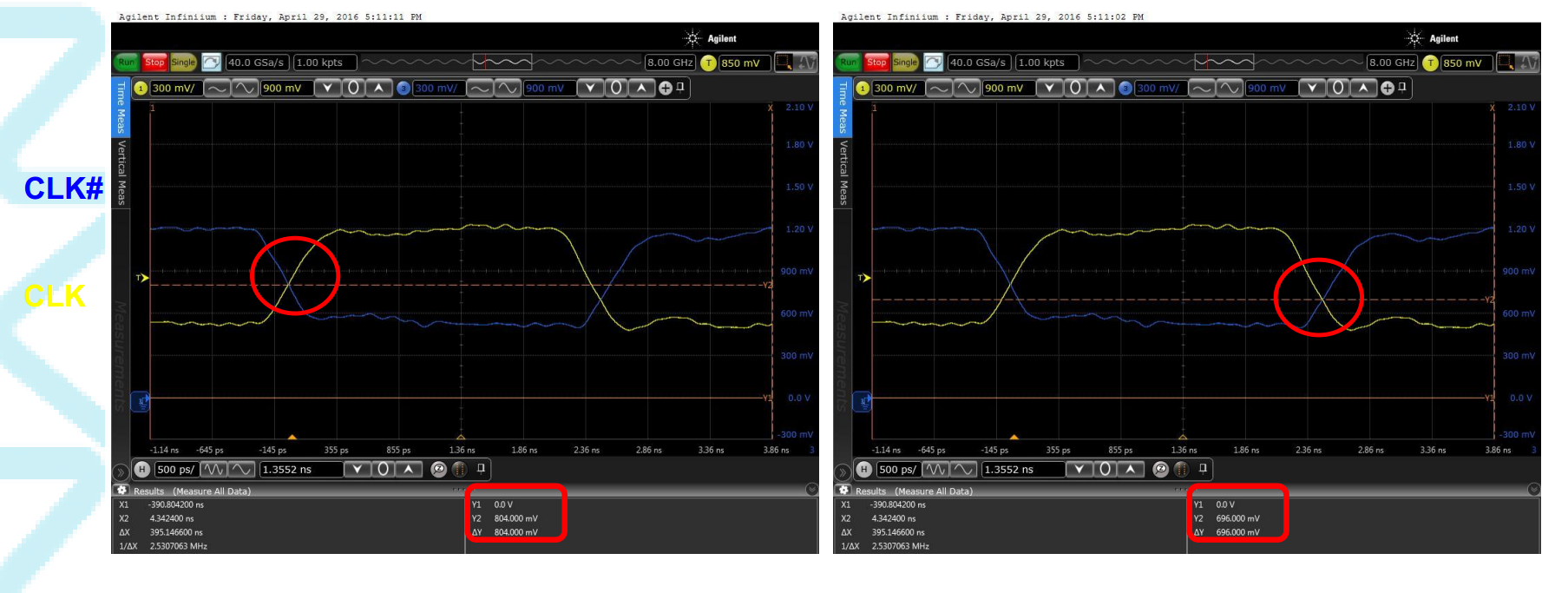

近期有点个项目,DDR部分不太稳定。让DDR芯片厂做一下时序分析。发现DDR CLK的正负交汇点电压偏低(如下图所示)。想请教一下名位大神,像这种情况怎么改善,这种情况对DDR的稳定是否有关系呢?

應該不是這個問題。

依波形圖看,Clock 頂多幾百 ps 的 jitter,對於 5 ns 周期的 clock 應該不會有問題。

應該不是這個問題。