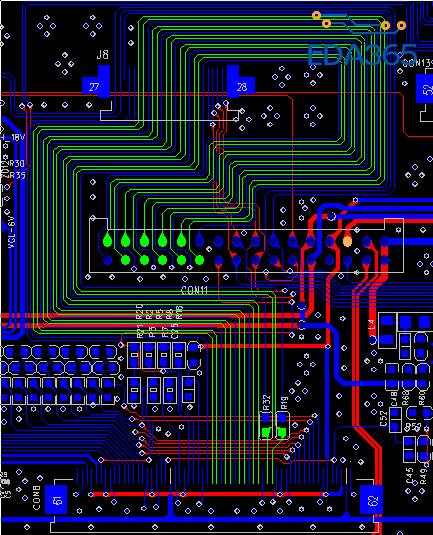

急!LVDS走线请教

时间:10-02

整理:3721RD

点击:

请问LVDS走线,这样绕会不会有干扰?

差分对之间有地就更加好,你这个不会有问题,

LVDS走差分为啥要绕圈?如果直接走过来打孔就好了。 差分下面不要走电源,哪怕正交也不行,做到差分 有完整的参考平面最好

1、这样绕线是没有问题的,不过为什么会都一个圈;2、差分线从连接器出来的地方为什么不走成紧耦合;3、包地线太长没有地孔,推荐400mil加一个地孔,并且做到完全包地

目测,这好像也没按差分走啊

3个插座,这样线序确实很顺。优点:同层走线,减少了阻抗不连续点

缺点:走线拉长,增加损耗的同时,也增加了Noise风险

优缺点共存,你的担忧完全可以通过仿真来解扰,各种方式的风险点对比一下,就有结果了。

学习了

大神好厉害

目前大家对于包裹地线的做法争议颇多,认为干扰可能会通过旁边的地线发散出去,造成更大的EMI问题。

单从板卡走线来看不会有大问题,还是要看信号的种类。做好信号的回流和参考,起码同层走线会减少阻抗不连续点,减少反射。但是不明白为什么要绕线呢?有时序的问题?如果有,绕线还是很有讲究的,不同的绕线方式造成的回路损耗与插入损耗都不同,向楼上所说,如果项目重大,最好仿真一下!

感覺...不是很好....! 1對....線有等長嗎?