DDR2地址线仿真碰到的问题

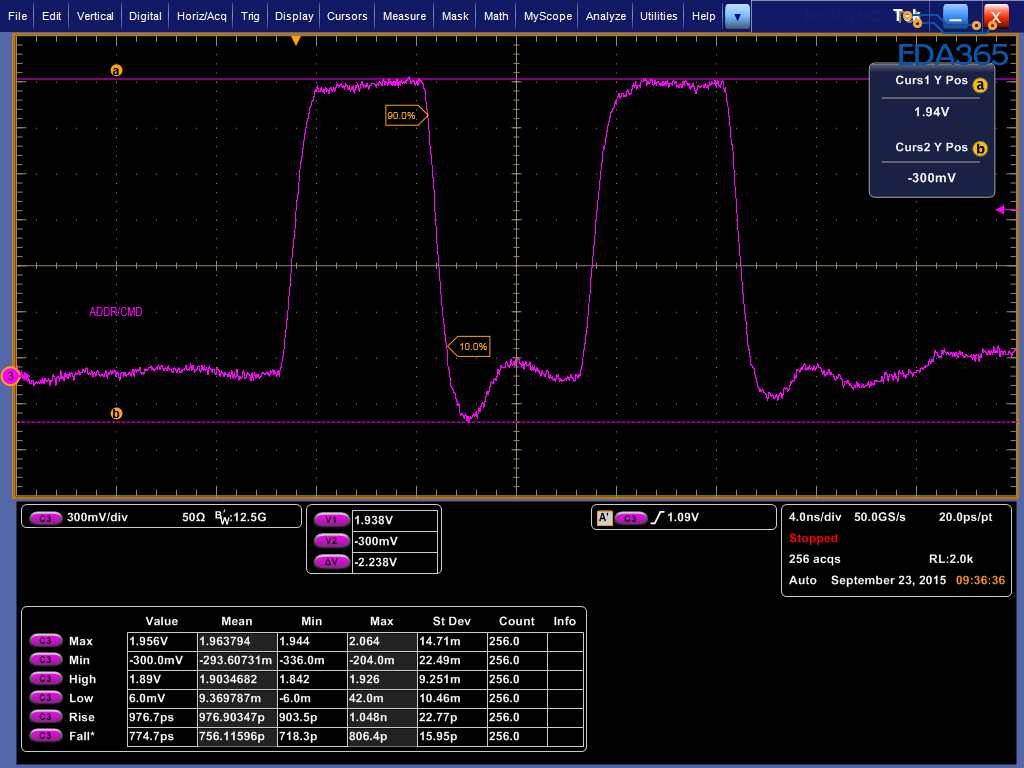

背景介绍:我们信号完整性部门测试DDR2的地址线和Cammond线的overshoot/overshoot area超标,软件已经将驱动能力设置到了最低,实际测试波形如下

由图片可知,undershoot虽然看上去有俯冲,但是没有超标,overshoot看上去没有过冲,但是却超标了,再仔细看图片,原来波形的高电平竟然达到了1.9V,而示波器的软件是按照1.8V作为参考来计算overshoot的,所以问题出现在高电平的幅值上面,我推测原因是因为没有加VTT上拉。

由图片可知,undershoot虽然看上去有俯冲,但是没有超标,overshoot看上去没有过冲,但是却超标了,再仔细看图片,原来波形的高电平竟然达到了1.9V,而示波器的软件是按照1.8V作为参考来计算overshoot的,所以问题出现在高电平的幅值上面,我推测原因是因为没有加VTT上拉。于是我利用刚刚学会的反射仿真来是试一把,可是,现实非常地打击人啊:(,下面是仿真碰到的问题,请大神帮忙分析:

1)我在allegro里面设置好元器件的model,然后直接将网络的topology拽到Sig xplorer里面,仿真出来有两个地方都和实际波形不符合,第一个就是上升沿竟然也有很大的俯冲,第二个就是,最终电平竟然稳定在了1.8V

2)我打开sig xplorer,直接在里面构建拓扑,仿真出来,电平倒是稳定在了1.9V,和实际测试差不多,但是上升沿还是有过冲,和实测不符合。

求大神帮忙看看我哪里出问题了,折腾了2天了,哎

多谢多谢

小编,你好,能不能描述下如下问题

1 给出你所测信号的拓扑结构图,各个部分的线长最好标注下

2 给出你测试波形上的测试点,就是说你整条链路上的哪个点测试得到的波形

3 实际ddr运行的参数设置,比如driver设置的是什么类型等

4 说下你的测试条件,比如示波器带宽,探头选择等

呼唤大神们啊

这个就是实测和仿真的差距。有这种差异是很正常的,毕竟你的参数设置不一定一模一样,另外,你的设计DDR2的仿真和测试所使用的模型(实际使用寄存器改变,仿真是手动调整)有可能还不一样。后面的就看你自己悟了。

有些情况是仿真不出来的,你的供电电压是不是太高了

从图上看,上升沿比下降沿缓,所以下冲要比上冲严重,那么上冲不明显就可以理解了

我的DDR VDD是1.8V,很准确,我测量过了。为什么地址线是1.9V?,难道是由于探头的接地点选择的不好?有电压轨道跌落?

我猜是你的驱动电压设置问题。

这与你的VDD有什么关系呢?照你这样说,电源正确,板子就不会有问题了。

VDD电压很稳跟号信的Overshoot没有必然的关系,Overshoot过高只与信号线的匹配程度有关,匹配的好,Overshoot较低,反之则高。上升和下降沿本身存在速度不一样,那是与Driver端上下MOS的开关速度不一样有关。仿真的结果与测量值之间的不一致,应该考虑你的模型是否精确,以及信号线建模是否精确有关。

都不实际跑下仿真就给建议,果然都是大神,然后结果呢?问题怎么解决呢

这个回复点赞,这才像解决问题的样子

icy88你好,抱歉,你回复的如此神速,以至于我没有看到你帖子,还是别的兄弟引用我才注意到

我的topology如下图所示:

示波器的探头是放在了VIA11,或者VIA12上边

DDR2的driver已经通过软件设置到了minidriver,仿真的时候也选择的minidriver模型

示波器的和探头的带宽都是12G,实际测试波形如下 :

另外,需要说明如下,软件设置驱动能力最小,实测波形和仿真差距比较大,软件设置成HSE模式(这个模式按照规格书就是最小驱动模式),实测波形和仿真比较类似,但是过冲的幅值不太一样

了解啦,谢谢