DDR3 地址组VTT上拉等长的问题?

最近在布一个DDR3的片子,以前使用的都是LPDDR,可以不用VTT上拉,直接所有线组等长即可。

现在使用的DDR3的片子追求质量要求VTT上拉,我已经把所有的线都做了等长,最后把地址组的都接到VTT上拉上,接好后再将地址组的十多根线等长,不知道这样行不行?

还有我的DDR的数据组和时钟组都是870mil,地址组本来也是870mil,由于要接上拉电阻T型走线,线长了变为了1040mil。,不知道这样可以不?内存是海力士的DDR3 800M!

大家讨论一下吧!

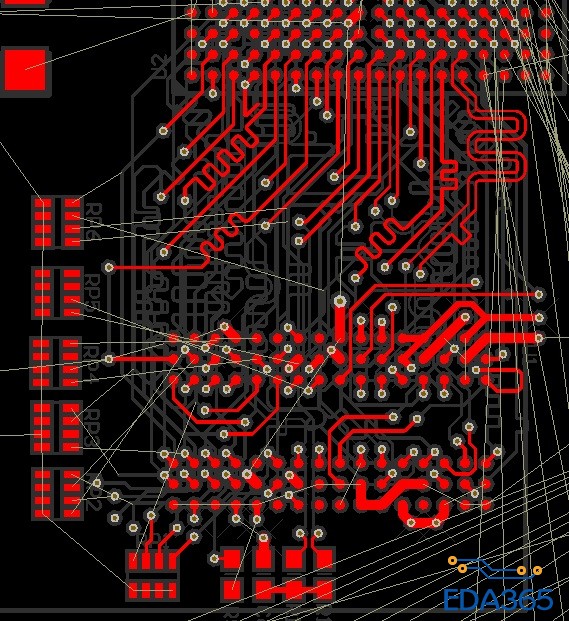

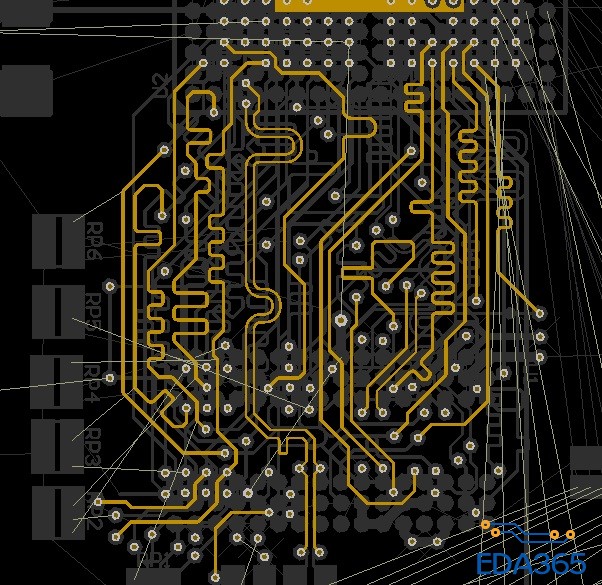

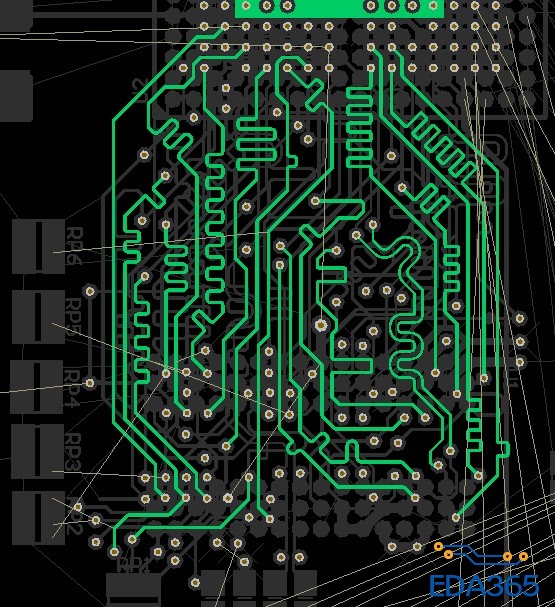

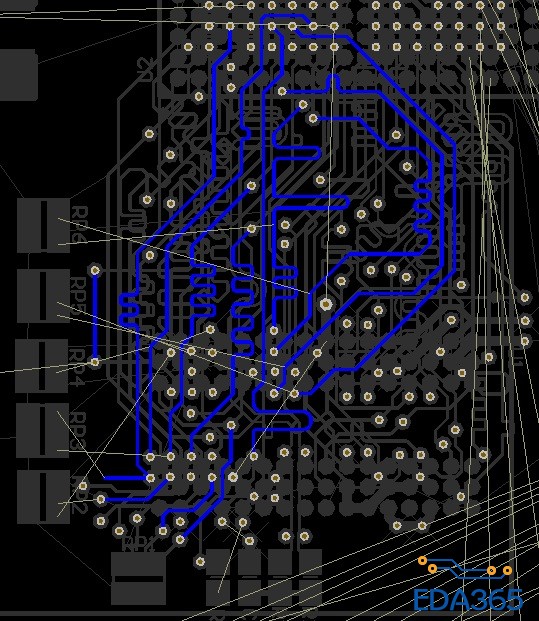

下面是我画的各层走线,底层左下角有几个组派就是VTT的上拉电阻。我是把所有的线都等长完了,再画的VTT上拉。打算随便找个地址组上面的过孔就往VTT电阻上面连,连接完了再做地址组等长,不知道可行不?还有地址组比其他组长可行不?

给点意见吧,各位!

1、接好后再将地址组的十多根线等长,不知道这样行不行? 接上VTT后不用再等长了。

VTT不等长可以的,可以改write leveling。

只要到SDRAM的pin上登长就可以了,pin之后再接VTT,这段走线不等长没关系。

其实对于DDR3信号来说,主要是CPU到SDRAM之间等长,他们俩之间等长了,时序就对上了。VTT的作用是,当信号为"1"时,电流从1.5V电源经过上MOS流入VTT,而当信号为“0”时,电流从VTT经下MOS流入VSS。

我理解就是CPU到内存的传输时间一样就行,VTT上拉可以理解为中间的一个分叉,不影响CPU到内存信号走线的长短,最好是把VTT上拉的分叉也给等长了!网上有个说法是VTT的分叉尽量靠近内存,尽量短,不知道有没有这个说法?

是的,VTT尽量靠近SDRAM端,这样可以减少stub,而且在最末端接VTT,这样的影响就要小很多。

上拉后还需要等长吗?没上拉之前已经做了地址组等长!

感觉你这个800M数据率应该没问题.如果800M是时钟频率的话建议还是稍微优化一下.

1.数据线最好同层,不知道你的MCU芯片是什么,怎么这么乱,都不做DEMO的吗?还是你这边需要优化一下;

2.DDR3数据和地址需要不需要做等长,主要看你的芯片本身支不支持leveling功能;如果不支持在500mil内都没问题,当DDR2来做; stub肯定越短越好了; 上拉那段越短越好,小于500mil; VTT处加0.1uf电容若干;

3.其它实在没什么要注意的了,因为你只是1驱1;很难出问题的.不过我是觉得地址线的上拉完全没有必要,物料成本会降很多.看样你们的产品应该不会批量..

个人感觉只要地址线自己等长就OK了!

Data走线每个Byte控制等长;

感謝分享~~