芯片端口阻抗变化

时间:10-02

整理:3721RD

点击:

在使用某家公司的芯片的时候通过TDR发现其RX端差分阻抗80k(近似开路),而TX端差分阻抗120欧姆。 不管芯片是否上电都一样。

联系其FAE,其说法是通过对芯片寄存器配置可以使芯片IO口阻抗变化。实测发现配置寄存器后TX端阻抗在100附近,但是RX还是在很大的范围内变化。他们说这是正常的,不会影响,包括华为都在用。

请问大家有没有发现类似的问题。 一般情况的使用的芯片不管上电与否的情况下IO口阻抗都能保持在100欧左右。但是这款芯片不同。请问为什么?

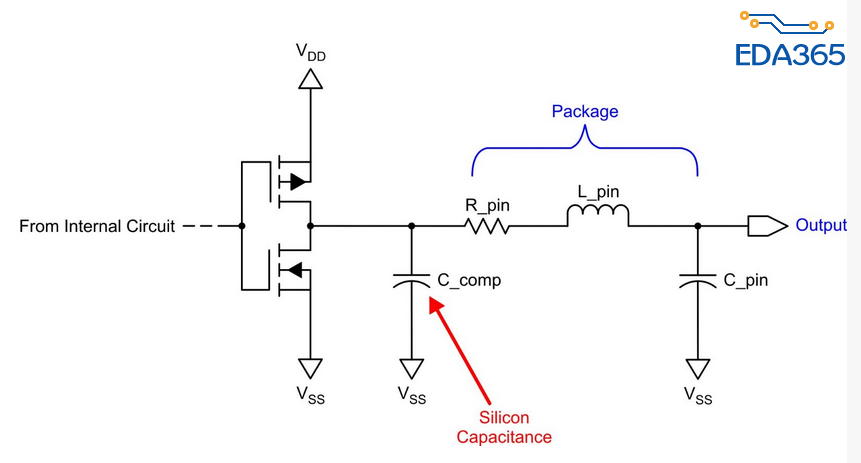

输入端等效电路,一般输入端没有模型也可以仿真

联系其FAE,其说法是通过对芯片寄存器配置可以使芯片IO口阻抗变化。实测发现配置寄存器后TX端阻抗在100附近,但是RX还是在很大的范围内变化。他们说这是正常的,不会影响,包括华为都在用。

请问大家有没有发现类似的问题。 一般情况的使用的芯片不管上电与否的情况下IO口阻抗都能保持在100欧左右。但是这款芯片不同。请问为什么?

输入端等效电路,一般输入端没有模型也可以仿真

RX 部分的输入阻抗我们默认为都是>5K 欧的,你去看看输入端的IBIS模型的等效电路,就是2个钳位二极管,

所以没有接收端的模型我们都可以仿真。

如 CML LVPECL LVDS电平的输入输出引脚电路,会有一电流镜的,然后是端接电路。

当然此芯片的接口结构数据手册没有,原厂也不提供。他们仅说过非常复杂,不影响使用。