PI Z阻抗分析 做法解释

时间:10-02

整理:3721RD

点击:

我见过有人做Z阻抗分析时会在port一端加上0.001ohm的电阻,这样,仿真的曲线就全部在0.001ohm以下了。

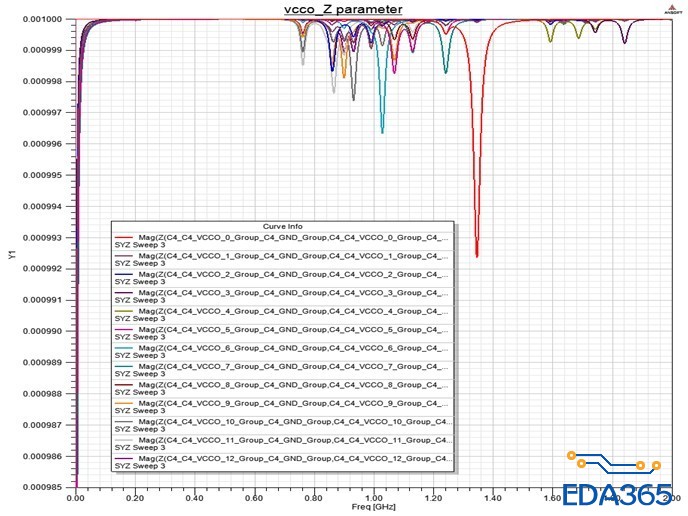

这种做法对吗?如下图效果:

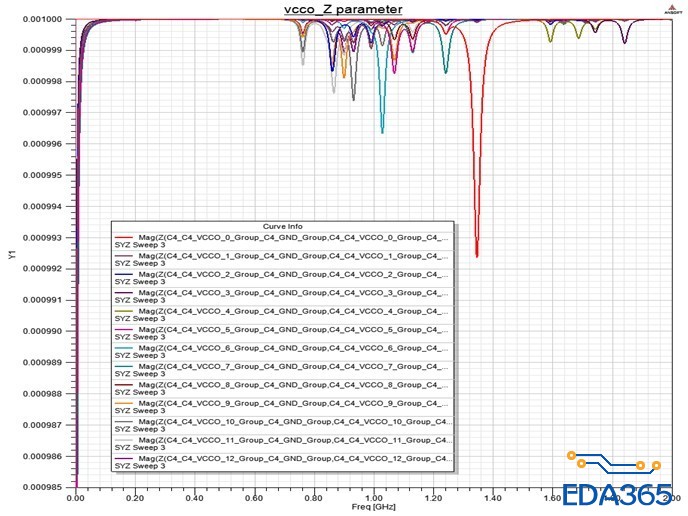

一般的方法,不加0.001的vrm ,则Z阻抗曲线为:

这个结果该怎么看?不知道他的Z阻抗有多大。另外目标阻抗是0.165ohm 工作频率400M

这种做法对吗?如下图效果:

一般的方法,不加0.001的vrm ,则Z阻抗曲线为:

这个结果该怎么看?不知道他的Z阻抗有多大。另外目标阻抗是0.165ohm 工作频率400M

vrm处做一个等效的0.001ohms电阻是可以的,代表上电情况下vrm port的等效交流阻抗。

但是不能加在需要测试的位置,那就没有意义了。

如果你不加,也没有错,你测得的值为未上电的情况。

信号的一端是BGA 另一端是FC

那就需要加在BGA端了?

学习中

学习 学习

把电阻加在VRM端是可以的,你的第一张图片应该是有问题,如果电阻没有加错,那么第二张图的曲线左边应该会往下掉,成为一条直线

甚有道理~~~~

后来发现,电阻应该加到BGA供电端

我们一般就这么干的。

这个干是看起来比较方便么?小编

应该是比较符合大众的眼光。

学习中, 以下为本篇阅读后之心得...

power与ground本为两个不同的net. 可视为两个不同导体.

从driver端(die, chip...)取z-parameter(可由s-parameter转, 如本帖所示).

(1). 若在另一端(VRM端)加上resistor(可视为VRM内阻), 则结果如第一张图所示.

若power/ground net本身的resistance也很低, 则整个PDS(power delivery system)

DC下的resistance应该很低, 将freq.取log scale, 应可在低频区看到平的直线

(...曲线左边应该会往下掉,成为一条直线).

(2). 若无外加VRM resistor, 则power/ground net可视为两个不同导体, 其所得的结果

应该与量测capacitor一般, 结果如第二张图所示.

以上....