信号跨电源分割现象解释

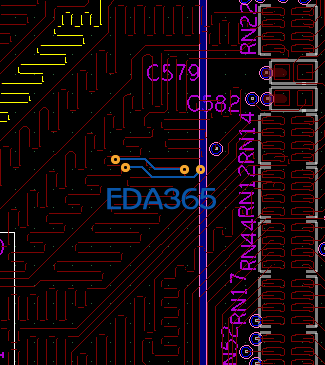

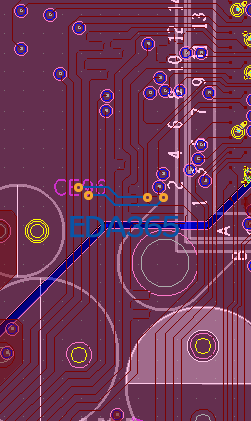

蓝色为分割线

四层板top vcc 层

我认为只要是跨分割平面不管是高速还是低速信号,都会影响它的返回路径,也就是影响了信号和回路构成的环路面积,而这个环路面积就相当于一个环形电感,根据电磁感应原理,高速信号通过时肯定是比低速信号通过时产生的磁感应强度高,也就是EMI更强,根据能量守恒,你发射出更多的能量,你自身受到的影响就越大,表现就是波形失真就越大,而你的高速信号能不能跨区,就取决于你能不能承受波形失真带来的影响,高速信号跨区分割肯定会使EMI增强,毫无疑问这个,低速信号也会增强,但是强度没有高速的高。

你自己都说了,那是低速信号

什么样的信号算是低速信号呢?

通常的经验是:连线长度小于信号上升沿有效长度(Tr*Velocity)的1/6(也有用1/4的,或者1/sqrt(2pi)的),我们就可以把这个电路当作集总系统来处理, 或者反过来说,在这个系统里面,我可以把这个信号当低速信号处理.

你的意思是在这个长度上,高速信号也可以跨分割了?

求高手解答

解释的很好,有点明白了,谢谢啦

你说的跨分割区域,带来EMI吗? EMI问题是造成高速信号失真的原因了?

任何信号都能容忍一定的畸变,信号不可能无失真的传输,只不过是失真大小问题。

有些信号噪声余量大,容忍的噪声就能大点,有些信号非常敏感,一点点畸变就会影响系统工作。一个3.3V的IO信号如果出现两三百毫伏噪声可能不会有问题,如果一个10Gbps高速串行信号叠加这么大的噪声,系统就瘫痪了。

能不能跨分割,和这个信号是什么信号有关。如果你的信号速率很低,上升时间一两个ns,跨分割可能没问题,如果10Gbps高速串行信号跨分割,估计死定了。

上升时间很长(ns级),跨分割的影响可以通过PDN系统的设计最大限度的减弱,电路正常工作的概率很高。

我的意思是信号失真引起的EMI,Anfoft的一篇文档上提过EMC=PI+SI,也就是说PI,SI出问题都会引起EMI

哦,知道了,就是说跨分割,只要是信号,不管上升沿快也好,慢也好,在分割处肯定产生波形失真的,只不过程度不同而已,看是否能过接受的范围之内了?如果跨分割的话,我说的是速率不快的情况下,是通过仿真来验证的吧,不然冒然跨分割,板子制成后,信号验证失真,损失就大了

首先非常感谢于博士在百忙中来答复我的问题,我有一点不太理解,分割层的层面就是电源平面,那PDN系统还能如何改善这种跨分割问题呢? PDN系统是一个电源供电网络,电源平面就是供电层,不知道说的对不对?

如果PDN系统在较宽频段内都有低阻抗,对跨分割的影响有一定的减弱作用。分割平面相邻层有一个完整的GND平面也可以减轻一点影响。这些都是PDN的作用。

PDN系统两大作用:1、提供质量符合要求的电源。2、信号的回流路径。你从第2点好好考虑一下就明白了。第2点最容易被忽略。

不是所有的信号跨分割都要去纠结对信号本身的影响,这是一个综合性问题,不是几句话能说清的。

谢谢于博士,PDN系统还不太明白,我再琢磨琢磨