DDR3大牛进

一块嵌入式板子,电源等问题已经排除。DDR3的时钟DDR_clk 600+M时系统崩溃,且必现,调整到400+M时系统稳定工作,LAYout各项等长都做的很好,电源分割什么的和人家的DEMO板都一样,刻就是出问题呀,这个怎么破,还有啥可以调的,请大牛给个指导啊,一个半月了

忘了跟大家说以下情况,系统崩溃之发生在跑业务的时候(大量数据读写),不跑业务的时候不会崩溃

1: 看看ODT是多少? 一般建议ODT60,或120

2: 2T模式打开,如果是地址出现时序的问题,2T模式会有帮助

3:自己的芯片,还是别人的芯片。自己的就要看IC内部设计是否有问题了!

就是跑不了高速率嘛。SI 或者PI问题

1、查一下信号质量问题,是否过冲太大。附上图片。

2、时序,等长,结合眼图

3、电源噪声。也附上图片吧

等长数据表我就不贴出来了

电源我们用台式串联稳压电源替代过,应该不会有问题

数据已于 14:39 保存10 秒后保存 保存数据 | 恢复数据 字数检查 | 清除内容 加大编辑框 | 缩小编辑框

附加选项

本版积分规则参与/回复主题 转播给听众

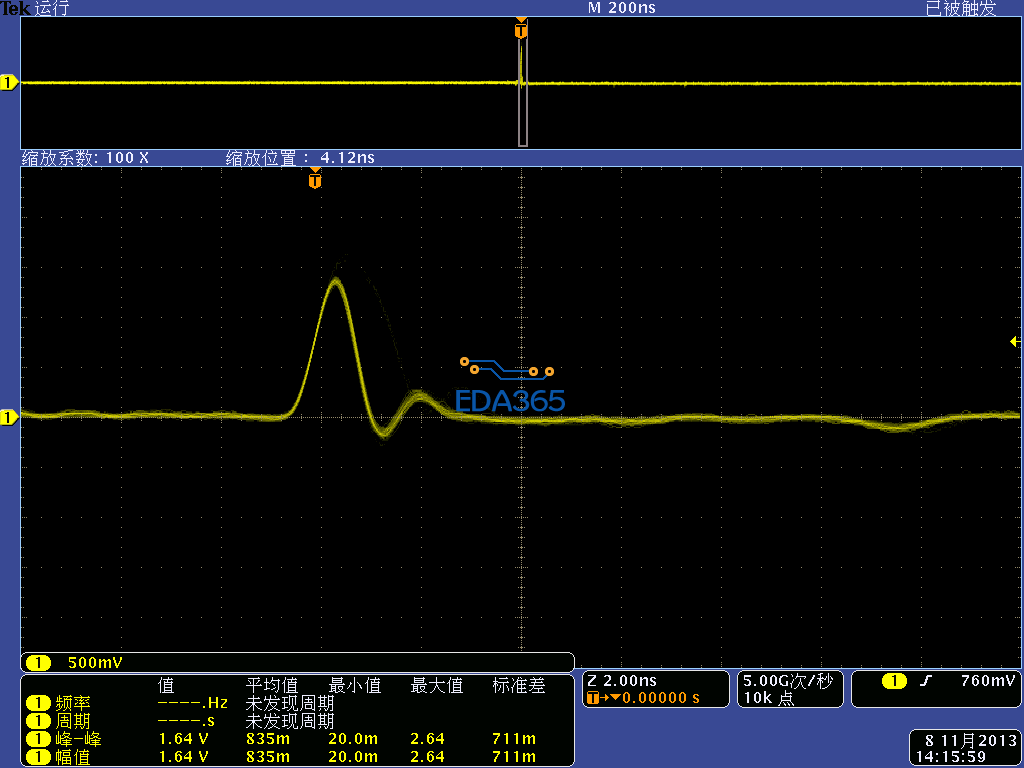

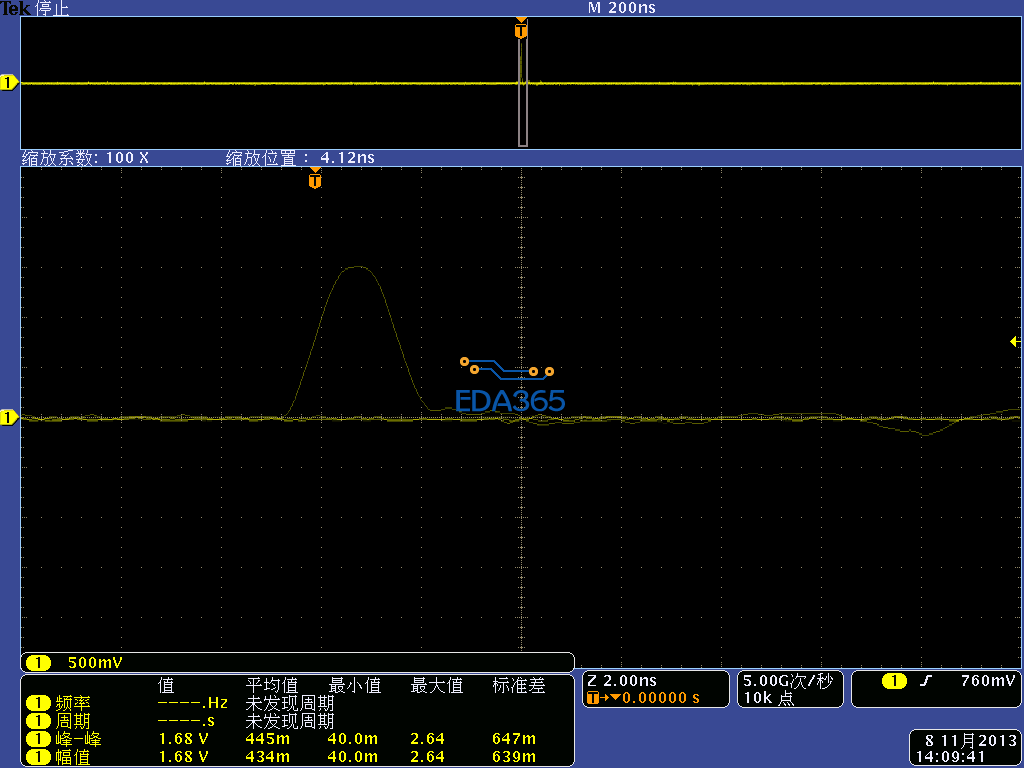

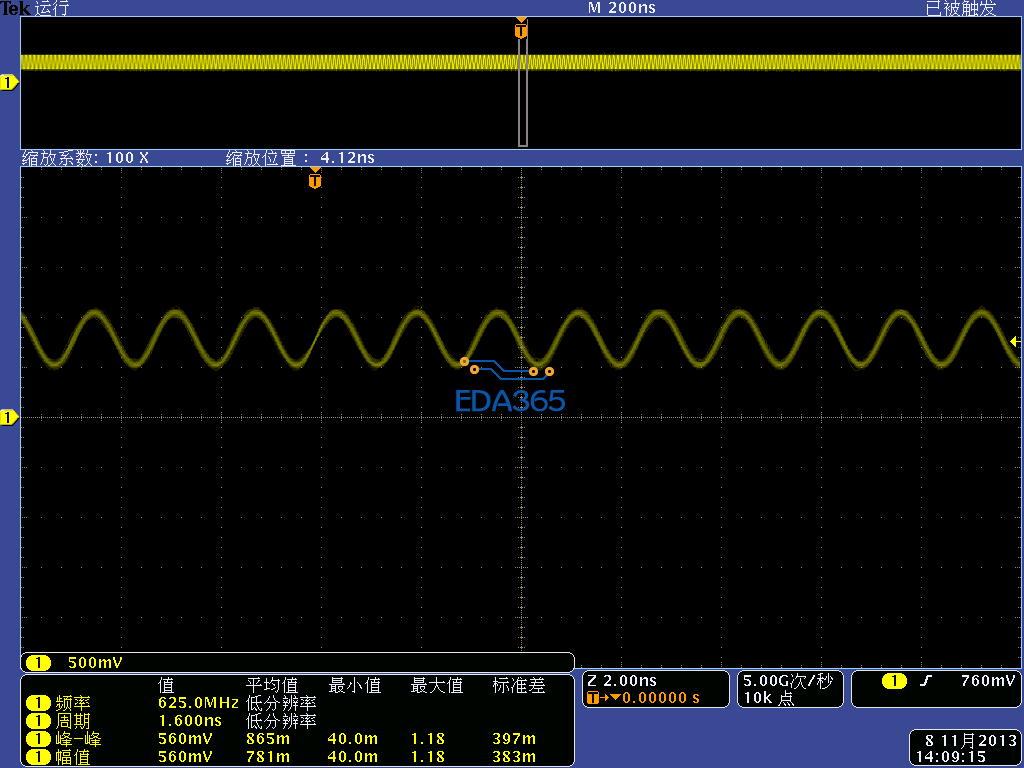

DDR_DQ0波形

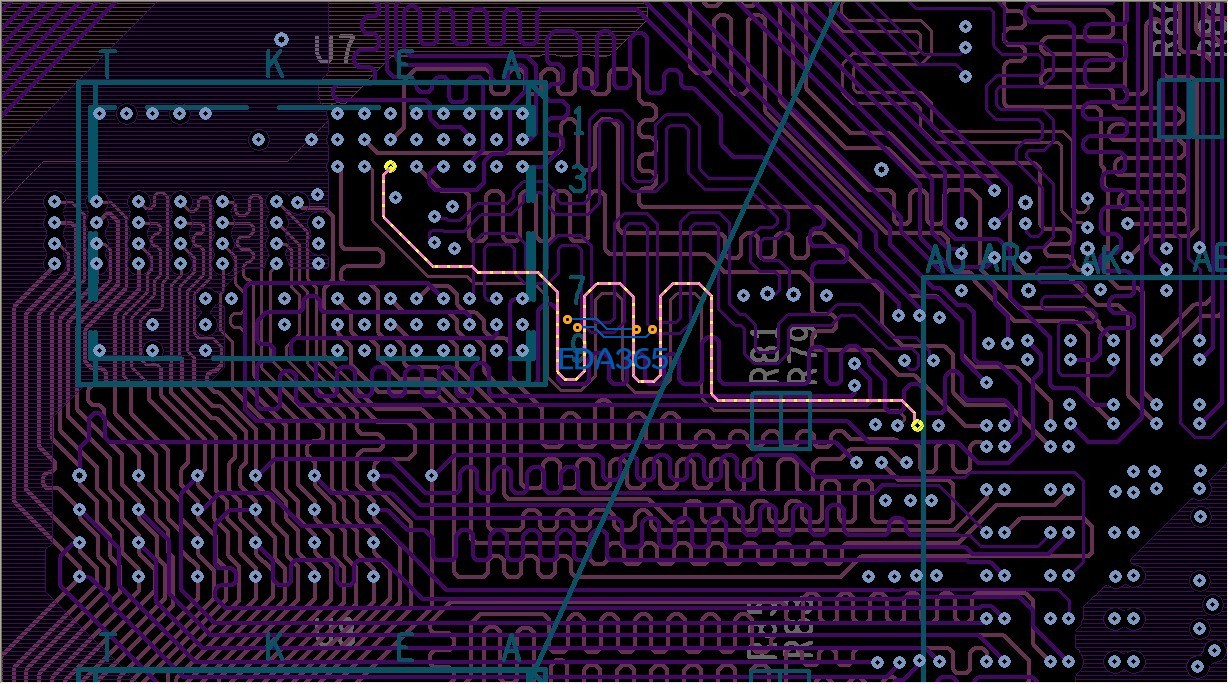

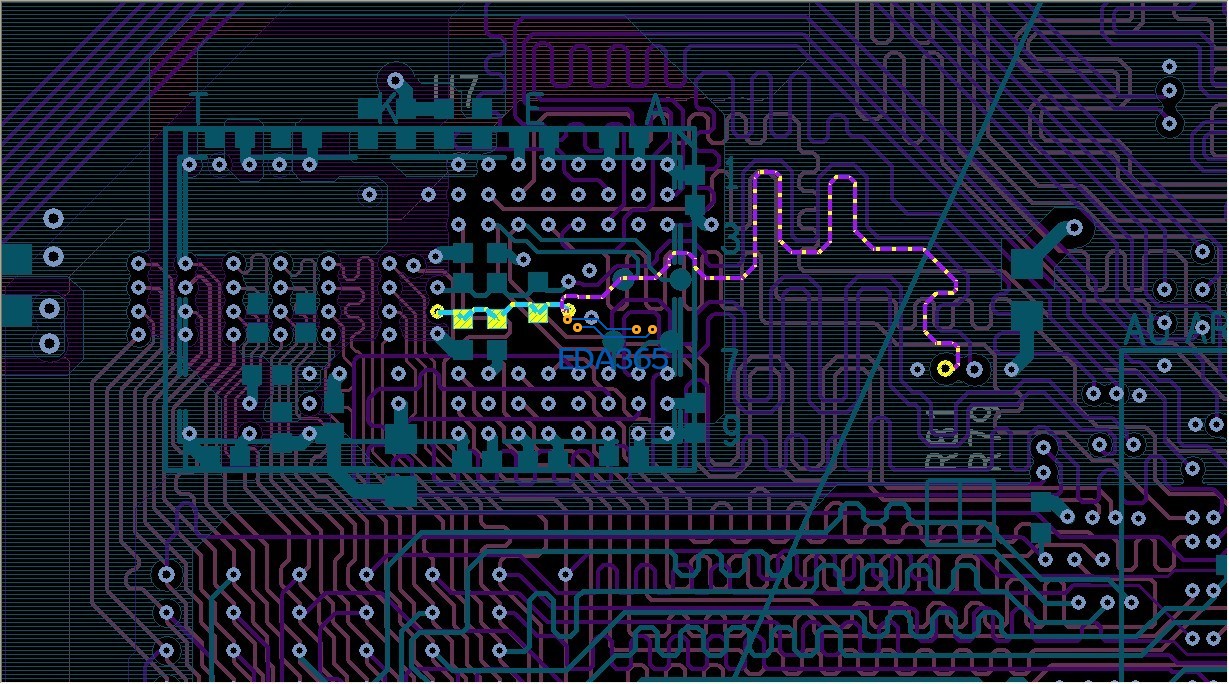

地址线DDR_A0走线

地址线DDR_A0波形

DDR_DQS0波形

DDR_DQS0走线

ddr_clk0走线

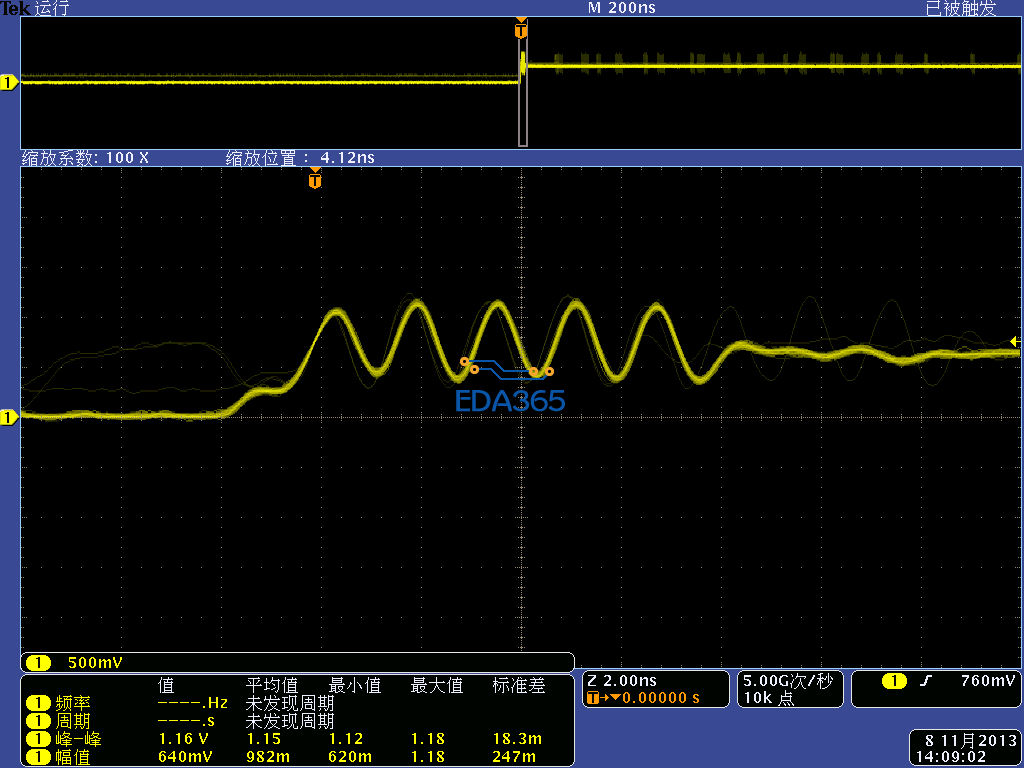

ddr_clk0波形

DDR_DQ0走线

贴的图顺序被打乱了,好像没法调整

我把波形图整合到一起,如图

系统崩溃后,地址线A0上的信号就没有了,但是CLK、DQS、DQ信号都还在

DDR3一般建议地址线走Fly-By,而且要有终端VTT匹配。如果走T型拓扑,VTT匹配应当放在T点处。

曾经把DDR3走成T型拓扑,VTT匹配放在T点处,时钟频率只能到400mhz,再往上就跑不起来了。

当然,不同IC的要求不尽相同。

我们的是T型的,不过这个应该没有问题的,之前在别的板子上已经屡试不爽了(同一个IC的解决方案),600+M跑的哗哗的,从来没有出过问题

如有 Layout 檔案,也許看看可以给你一點意見。

信號要這麼量,你量的電壓峰值有點小,DQ 信號也沒在 VDDQ/2 中間,怪怪!

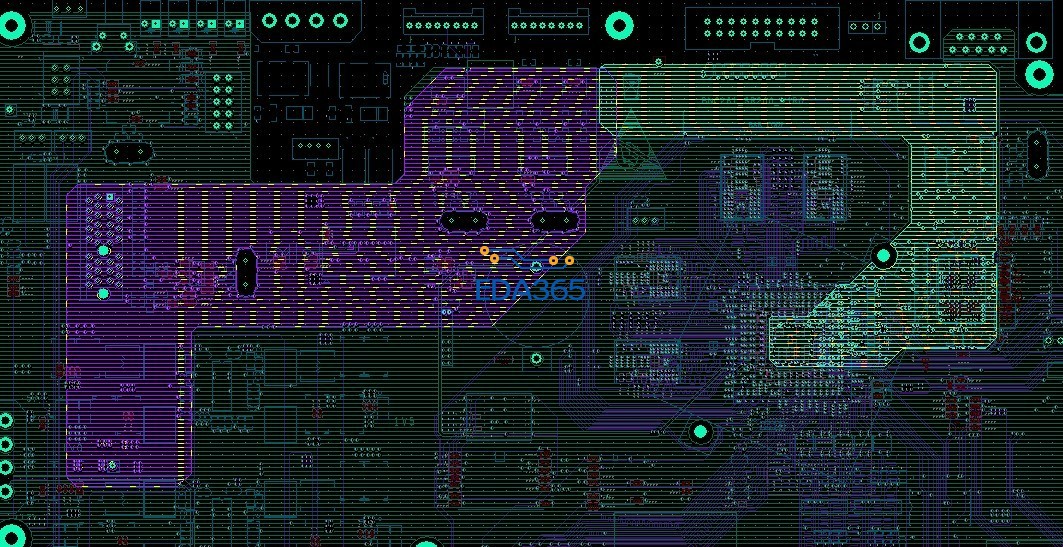

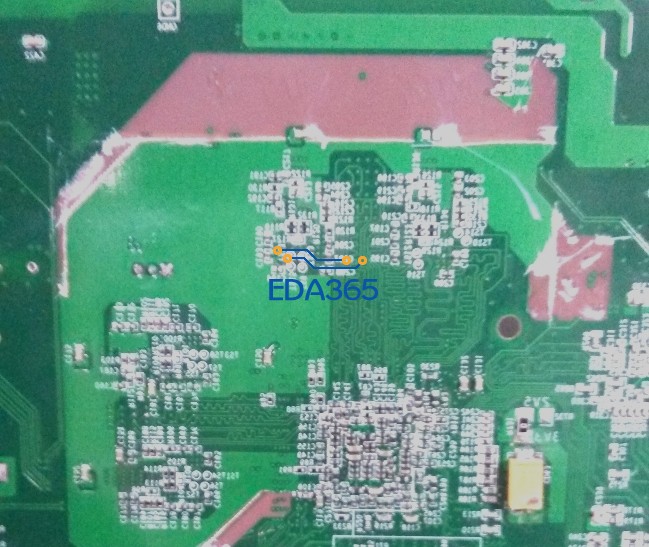

大家看一下我们的电源分割,图中高亮的铜皮是1.0V核心电压,左边是DCDC,右边是终端,紫色部分被割到第3层了,绿色部分在电源层,4片DDR被包围在里面。一致觉得这个不是很合理(这个我没办法),大家觉得会影响那么大么?

想知道是不是电源的原因,有一个办法。

1、你跑一下正常的速率,然后测一下1.5V的电压波动范围。一般在1.425V~1.575V之间是正常

2、你跑一下不正常的速率,然后测一下1.5V的电压波动范围。如果1.425V~1.575V间,可以排除1.5V电源的因素;如果在1.425V~1.575V之外,那电源是因素之一,这个时候要多加点电容,把电压范围调整到1.425V~1.575V间,看看跑不跑得起来。

个人意见……

都是牛人啊学习了

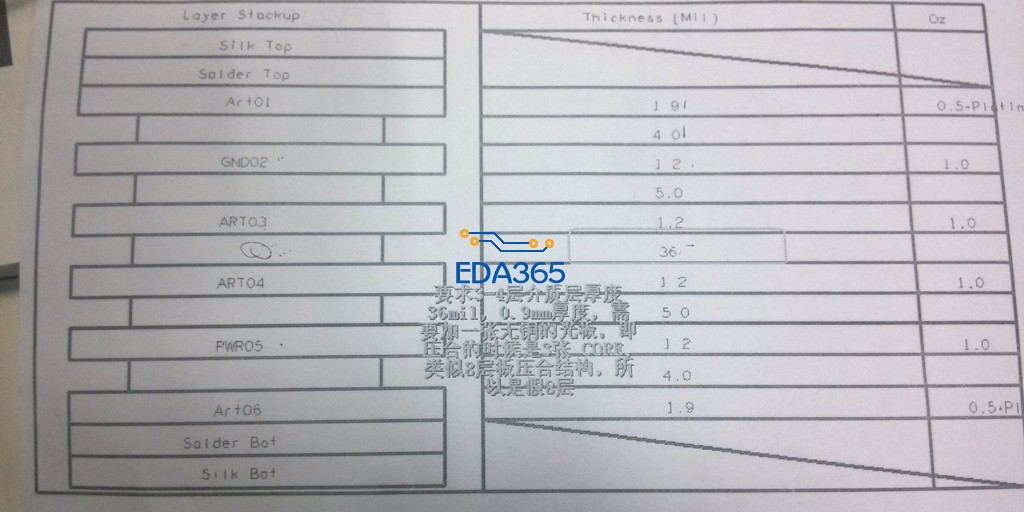

上传了叠层文件

Hi,Lkzui

For your reference.

honejing:

昨天切割了下铜皮,貌似不是这个问题

一點速度上的改進都沒有嗎?仿真可以看出這片 GND plane 在一些頻點有2xx mV 的電位差。

若不行只能實際量一些信號在判斷,可以先看寫DRAM 的 DQS/DQSB, Clock 對相位差。

另外要設法知道是寫錯或是讀錯?

或找出哪一個 DRAM 先錯,再抓問題。