正在看或者看过信号完整性分析第八章的请进

时间:10-02

整理:3721RD

点击:

本人正在看,有不懂得,所以想请教一下:

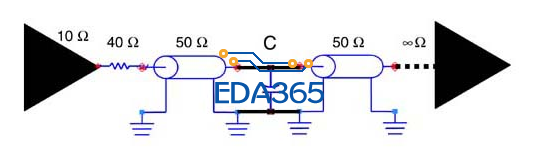

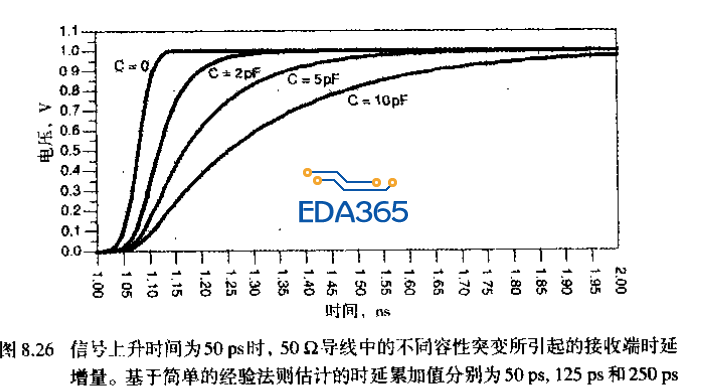

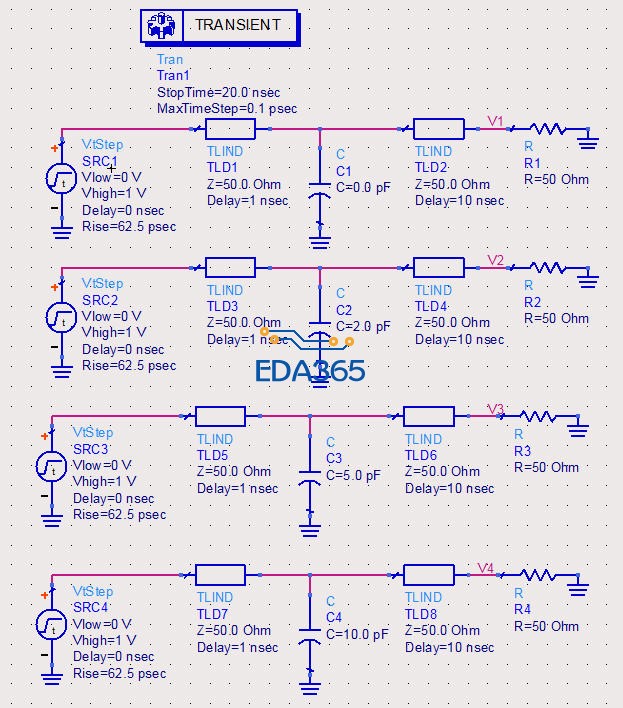

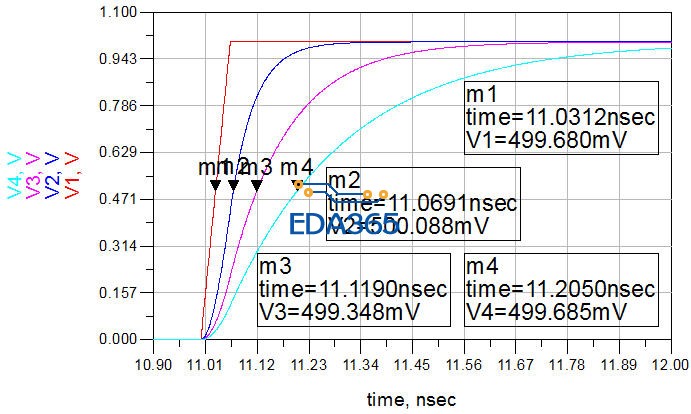

8.15节的容性时延累加。本人表示对图2中的C=2PF/5PF/10PF 不太能理解。首先书中公式RT10-90=2.2*0.5*Z*C;关于这个0.5的解释,我自己把它理解为连线中途的容性负载这样的结构,因为书上写了“传输线的前一半...传输线的后一半”。运用前一节的结论,不影响信号质量的中途容性突变C<0.004*RT,但是图2举例中RT=50ps,电容C为2pf 5pf 10pf不是远超这个限制了吗?我感到很矛盾。我特想知道的是怎么个电路原理图才能得到图8.26的波形(一模一样的),希望有仿真过的朋友给点信息

图片上不来。

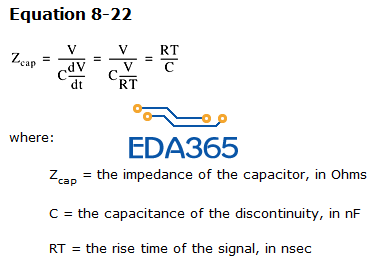

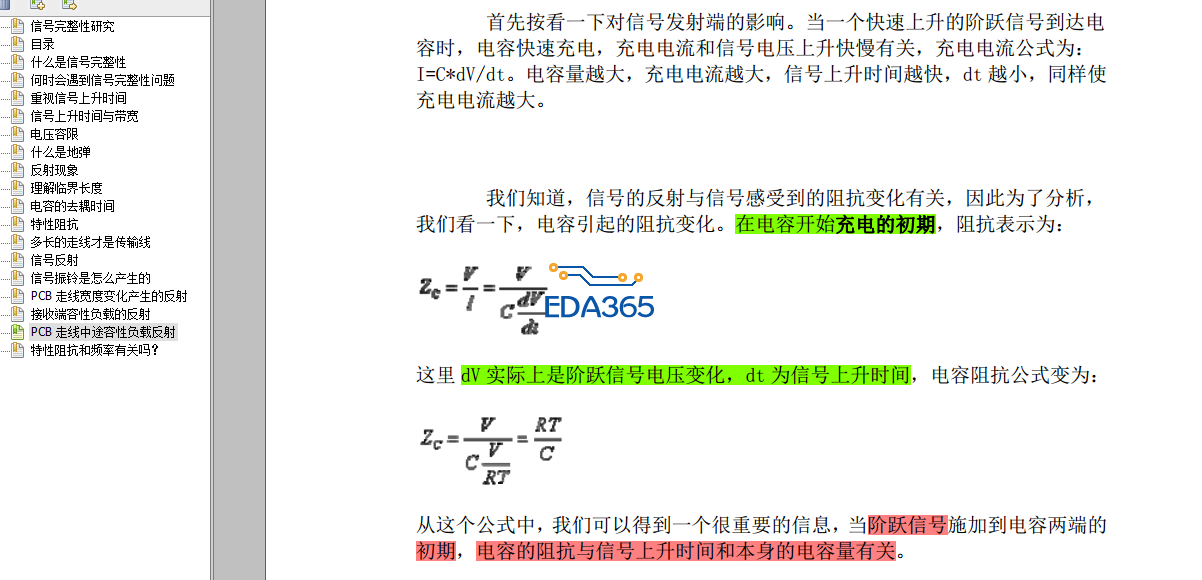

另外我还有一个问题想补充一下,下图中的公式是在书上8.14节 连线中途的容性负载反射 一节出现的,我只想问问这个RT是指最原始的信号的上升时间如50ps,还是指信号遇到中途容性负载,上升时间被延长后的、电容两端的电压上升时间,如(50+2.2*0.5*Z*C)ps?

公式

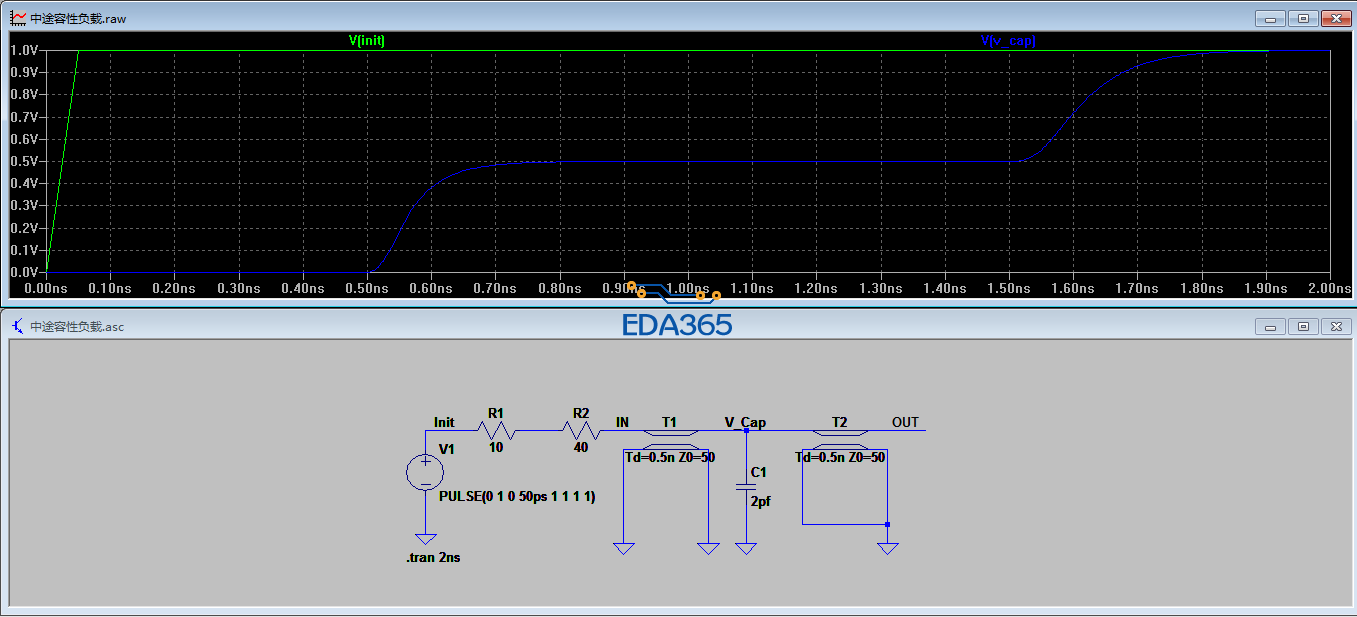

仿真

我这里做了一个,小编可以参考。

不过这里激励为理想step信号,上升沿为62.5ps(10-90%为50ps),容性延迟没有书中的那么大,这里的延迟分别为38ps,88ps,174ps

谢谢朋友你的回复,真的是太感谢了。不过我对电容那个上升时间什么的有着这样的理解。我觉得书上的意思就是说电容刚开始充电时,其阻抗确实是书上所写的那条公式,那个RT也确实是原来信号的上升时间,不过这也仅限于一开始的时候。到了后面,如果看回公式中的C*dV/dt,模电告诉我们这本来就是指电容两端电压对时间的变化速度。所以我就得出我前一句的结论“仅限于初始的时候”。不知道我这样理解对不对呢?

PS:还有那个仿真中RT=50PS 软件设置就要设置RISE TIME为60多ps那个,真是太贴心了,我也是在做了几次仿真后才突然发现这个事。再次谢谢你的回复

最后附上于博士说法,结束本帖:

学习了,我又要回去好好看书了。

这种容性的变化通常发生在过孔,走线拐角,以及连接器部分

能具体问一下吗,连接器是什么东西啊,能不能上个图,我经常疑惑跟我以为的是不是同一个东西?

连接器含义很广

有PCB与PCB之间的连接元件,有公座,母座,公插,母插,线材等

比如PCIE金手指,比如USB接口,HDMI接口,SATA接口等等

简单的理解就是任意传输线出现图形结构变化都会有容性的变化

公司内部上不了图,不好意思