DDR2数据线调试问题

1、数据线低8位能正确读写,高8位不能,在每次断电重启的情况下,高八位的读写结果不同,随机的。

2、地址线是正常的,我是在屏蔽高8位读写结果的情况监测地址线的,全部遍历64M空间都能正常读写。

3、用示波器观察高八位的数据线(在匹配电阻靠近DDR芯片端)上的写信号,数据线上有信号,且与低8位基本一样。

附件为高8位数据信号线上的写信号。

我现在怀疑的原因有两点:

1、DDR2芯片的焊接有问题,可能高8位数据接口相关的电源管脚没有焊接上,BGA封装,苦于没法检查;

2、时序问题,高8位和低8数据线的读写使能DQS信号是独立(分别为DQS1、DQS0),可能是高8位的时序不一致(布线的时候要求是一样的),示波器看DQS1差分信号很微弱,DQS0也是,没有明显的高低电平变化,这个很奇怪。

希望各位大神、有经验的同道帮着看下,给小弟点意见!

自己顶下!

ddr2的控制器高八位与低八位都有可调整相位的DLL,2的DLL值应该不一样,默认是一样的。调试时调完高八位的相位后再调第八位。调完后固定。

你好,谢谢您的回答,之前的问题后来无意中发现时DSQ1匹配电阻有一个虚焊了,所以高8位一直随机的,解决后,现在的现象更奇怪:下面是我对DDR进行读写全5操作,结果如下

地址 数据 数据

0x80000000 0x00550055 0x00550055

0x80000008 0x55555555 0x55555555

0x80000010 0x00550055 0x00550055

0x80000018 0x55555555 0x55555555

0x80000020 0x00550055 0x00550055

0x80000028 0x55555555 0x55555555

0x80000030 0x00550055 0x00550055

0x80000038 0x55555555 0x55555555

0x80000040 0x00550055 0x00550055

0x80000048 0x55555555 0x55555555

0x80000050 0x00550055 0x00550055

0x80000058 0x55555555 0x55555555

.....

读写全F,全A操作现象一样。就是高8位数据在地址低第4位为高时正常,为低时为全0。这应该不是地址线的问题...还可能是DLL相位的问题吗?

测试一下地址与时钟的关系,看看这几位地址的建立和保持时间够不够。是否地址与clk的相位不对。

我在读写屏蔽了高8位,然后对整个DDR空间遍历,没个地址写的数据不一样,依次递增,读回来都是对的,所以应该不是地址线的问题吧

DDR跑步起来吗,是的话就比较苦逼了。这问题难找

是啊,跑起来了,低8位的数据都能正常读写了...苦逼了好久了,问好多人都想不明白啊

DDR跑起来之前要测试是否有合适的相位,这个工作你做了吗,按照我说的做先低8位组,在高八位组,然后2个合并一起,需要写个程序,主要是读的,因为DDR需要去检测和锁定主芯片发来的CLK。写的话主芯片相移90,DQS对在DQ中间发出去的。相位写侧读,然后再去考虑写,用的是哪个厂家的。

是否把PCB的这一块发上来瞧瞧,是否SI/PI没处理好。

一定学会测眼图,这玩意儿一看就清楚的很。

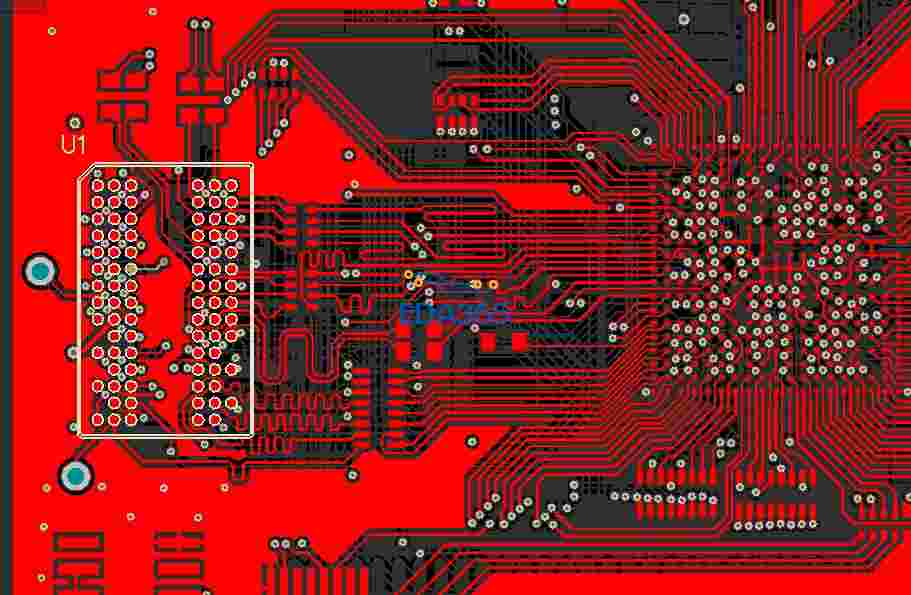

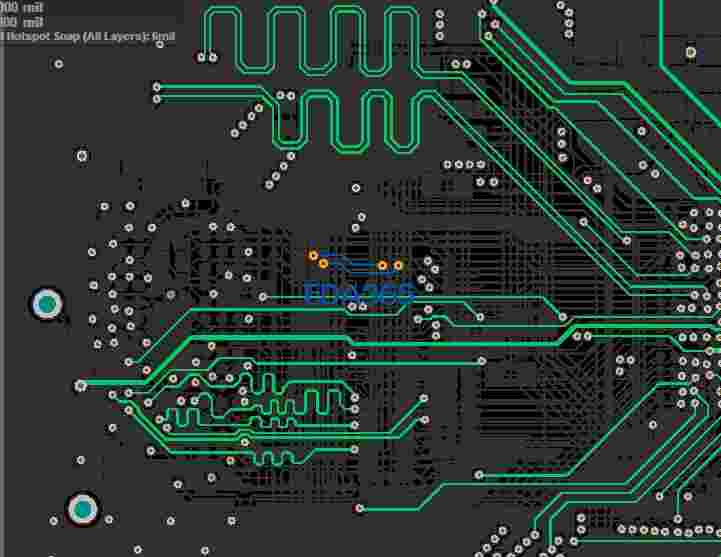

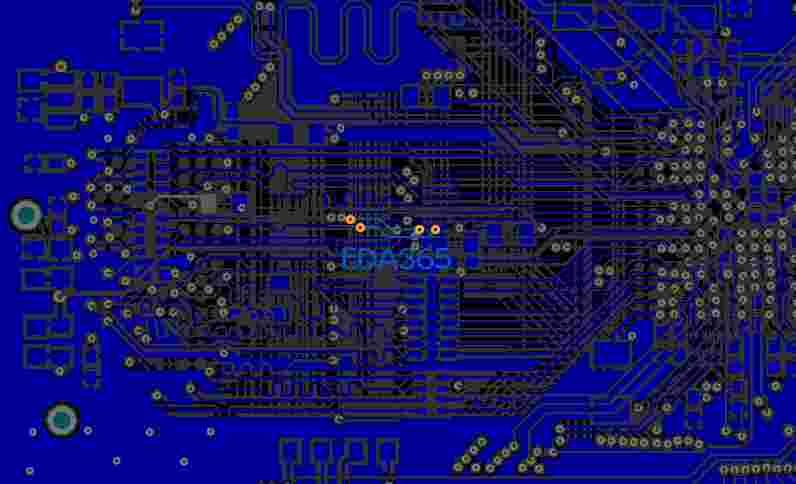

芯片是Micron的,DDR的布线用了三层(顶层,中间信号层和底层)如附图;谢谢您的指导,我开始认真测试下相位关系,眼图测试还不熟悉。

1. ) 先就 1# 楼的图说明,若以这个数据线的测试波形而言,这应该是一个无效的数据,它的信号变化只呈现在 0.9V以上, DDR2 的信号应该是以 0.9 V 为中心,往上下张开至少要 +/- 0.25 V。

2. ) 12#楼的 Layout 图而言,这似乎是一个没有考虑信号参考回流的设计 (除非还有参考层没有贴出 ),信号走线没有完整的参考平面,回流将到处乱窜,影响信号品质。

1、看规格书我也觉得这个信号参数奇怪,但是对比了一个正常的板子,同样的信号,也是这样的测量结果

2、参考平面有,整个板子有8层,中间分别为信号,信号,地,电源,地,信号

那可能是你沒有量到正確的信號,你的trigger level設在0V,可能抓到不正確的地方。通常我會用兩個條件來當觸發條件

第一用DQ再接著DQS@0.9V。