PCB上的差分线如何测量其阻抗

时间:10-02

整理:3721RD

点击:

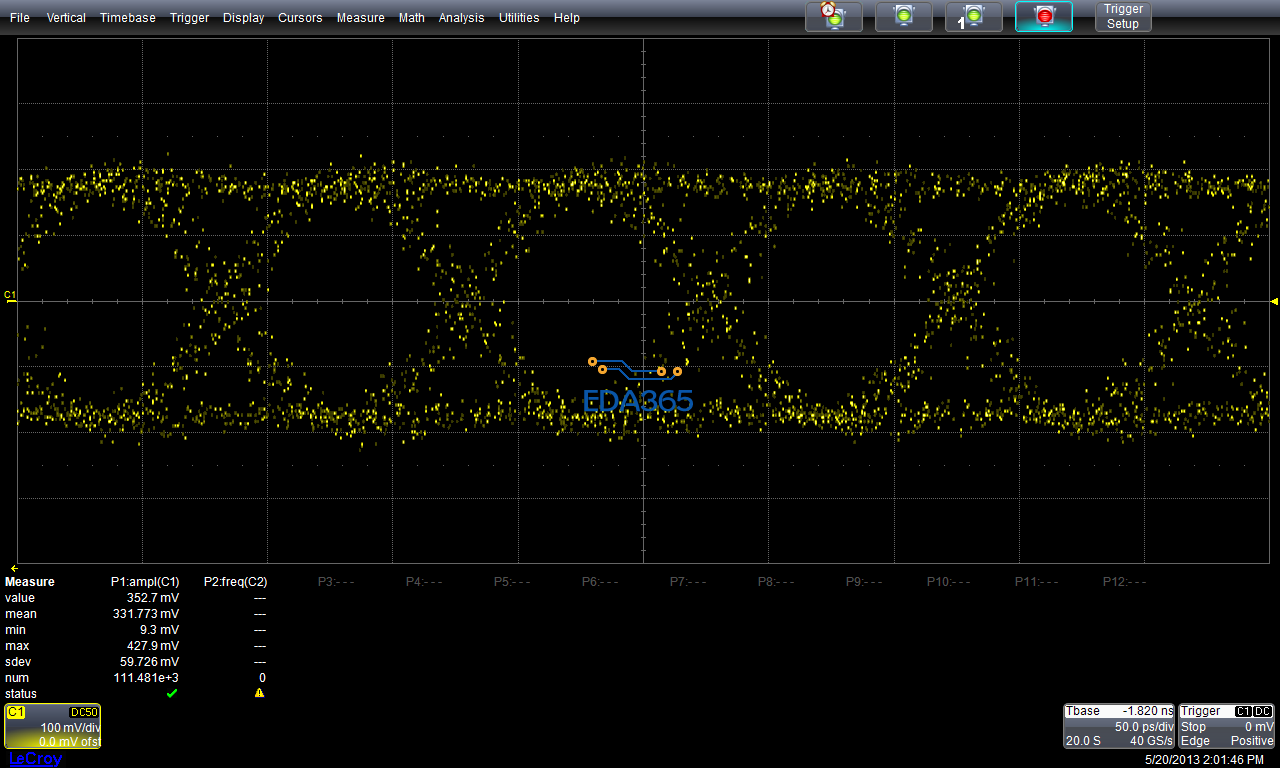

PCB板上一对10G的高频差分信号线,只取其一个单端信号(另一端终结),测量其眼图如下图1所示,

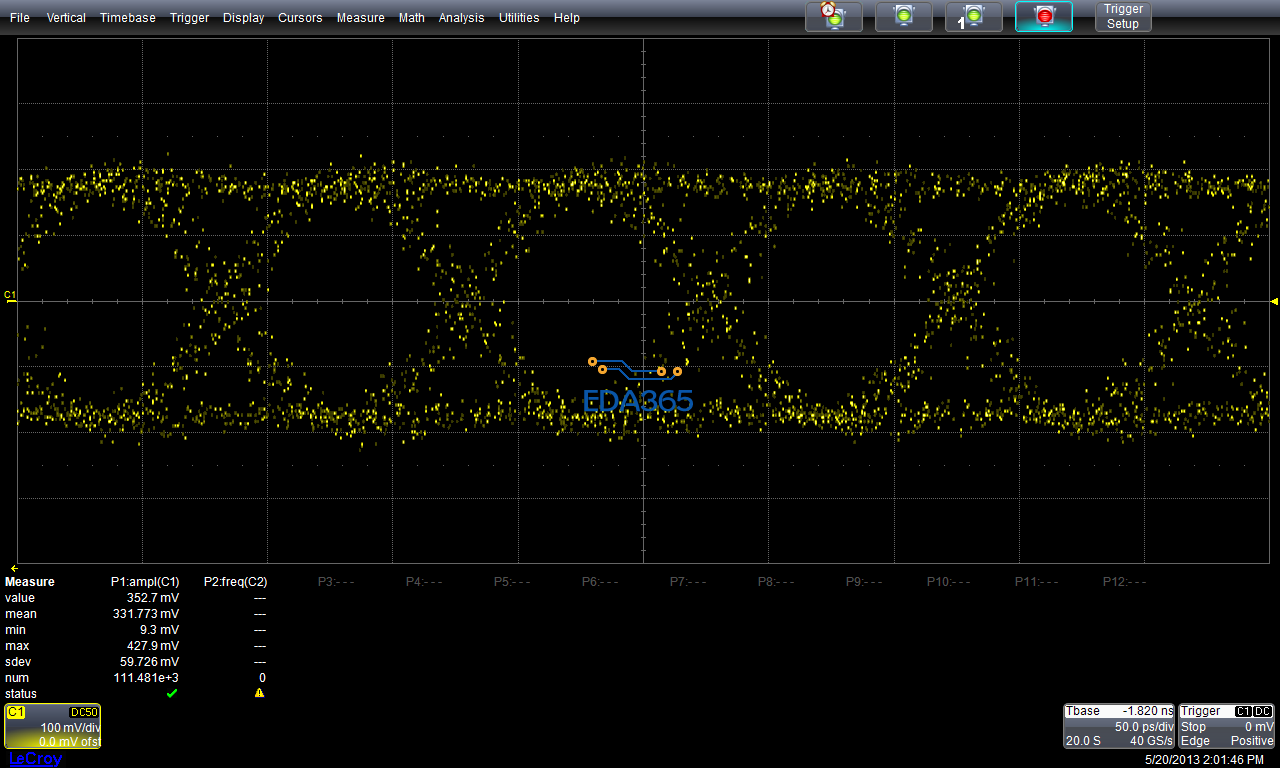

感觉信号质量还不错。然后将这一单端信号用同轴电缆与一个放大器相连,测量放大后的眼图如下图2所示,

这个眼图就明显的噪声很大。

噪声应该不是放大器引入的,因为用这个放大器,在同等条件下,放大其他信号源没问题。

问过其他人,说是被放大的信号源驱动力不足的原因造成,而驱动力不足可能由于阻抗不匹配造成,请问大侠们,我如何确定,阻抗到底匹配不匹配。

设计的理论阻抗是50ohms。

感觉信号质量还不错。然后将这一单端信号用同轴电缆与一个放大器相连,测量放大后的眼图如下图2所示,

这个眼图就明显的噪声很大。

噪声应该不是放大器引入的,因为用这个放大器,在同等条件下,放大其他信号源没问题。

问过其他人,说是被放大的信号源驱动力不足的原因造成,而驱动力不足可能由于阻抗不匹配造成,请问大侠们,我如何确定,阻抗到底匹配不匹配。

设计的理论阻抗是50ohms。

差分信号线是100吧?你怎么用50?特殊信号?

RJ很大啊

你的10G信号总线 是多少的阻抗?datasheet里面有说吧! 根据线宽,线间距,材料属性去算下阻抗就可以了啊!