关于Virtex5对DDR2的仿真问题,差分时钟怎么仿真?

时间:10-02

整理:3721RD

点击:

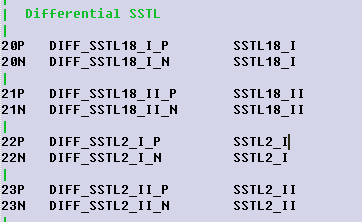

用FPGA控制DDR2,由于FPGA的时钟的管脚不支持DIFF_SSTL18,将FPGA提供给DDR2的时钟输出改成单端的,不知是否可以行通?请高手指教!

应该可以只要时钟频率够低200MHz左右。差分只是为了提高速率,增加抗干扰能力

硬件设计方面要注意一下

谢谢!

请教下你的FPGA模型是怎么弄的呢?

FPGA 只要电平标准一样就行了 差分电平和单根电平不一样的话看看能不能互相驱动,如果能互相驱动就改用单根电平的模型来做, 不能直接改差分的为差分的

一句话 什么电平用什么模型

在官网上下载的,然后再根据自己的需要,修改一下就可以了。

你试过用Quartus II产生的FPGA的IBIS模型吗?

没有

模型是有支持的