求教:Vcross电压对信号的影响

时间:10-02

整理:3721RD

点击:

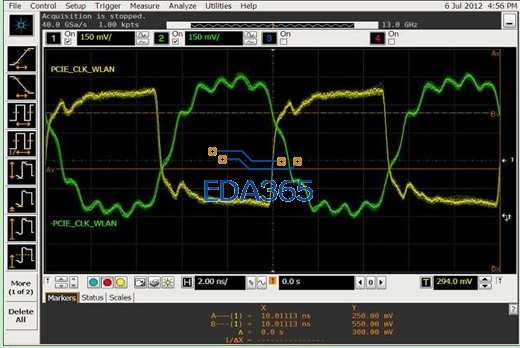

如题,Vcross这个参数该怎么理解?一般规范要求在250mV~550mV之间,现在测到的PCIE refclk 的Vcross在临界点。

不知道对信号传输有什么影响,这种情况是由于什么引起?该怎么改善?

真心求教各位大侠!

不知道对信号传输有什么影响,这种情况是由于什么引起?该怎么改善?

真心求教各位大侠!

顶起,急等~~~~~~~

的PCIE refclk 的Vcross在临界点会对时序有影响。

这种情况是由于估计是参考电压波动的原因。就是地弹引起的。

终于有人回答了。

我刚查了layout图,clk+和clk-的线长差22mil,不知道与线长有没有关系。

这种情况,会不会造成共模电压波动较大,从而造成较大的EMI?

你们这个线长差应该控制在5mil 以内,要不也会引起这个问题的。相位噪声太大了。

不懂,求指教?

请教 Vcross 是什么?网上怎么没查到这个交叉电压的概念呢

+-2个线波形的交叉点

去查JEDEC

应该是+/-不等长造成的,这样将会产生共模噪声,引起EMI