关于铺铜对于SI的影响

1、内电层尽量完整,有助回流。

2、表层尽量不走先,且铺铜,可以减小PCB对外面的辐射。

我的问题是:

1、内信号层,需要不需要铺铜,铺铜对信号有何好处或者坏处?

最近做了6410核心板,共8层,2层GND完整,1层电源。内信号层和表层都铺地处理了。结果DDR有问题,没有调出来,不知道是不是内层铺地的影响?

2、表层铺铜,唯一的好处就是防止对外辐射么?有没其他影响?

请大家探讨,还请高手不吝赐教!

我在内层的信号层上不覆铜,而是在内信号层的四周覆铜,但是离信号线很远,其它一样。覆铜原则依据信号回路来。

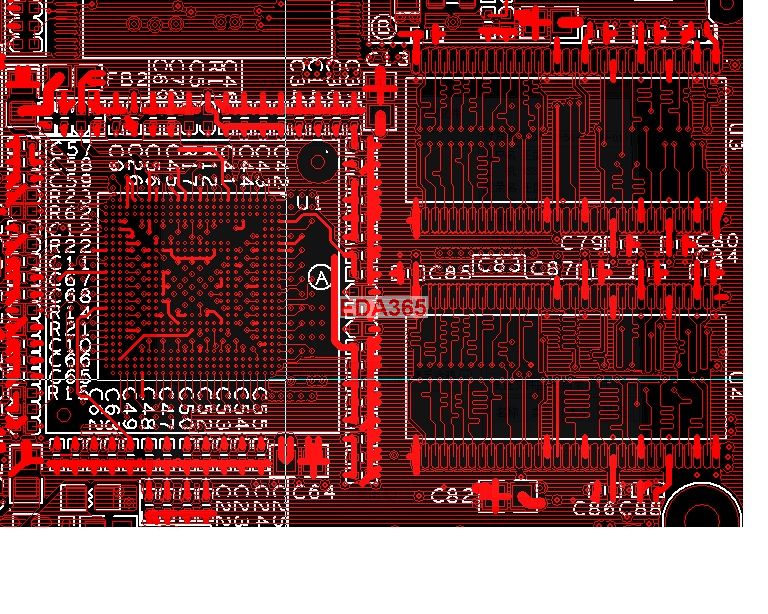

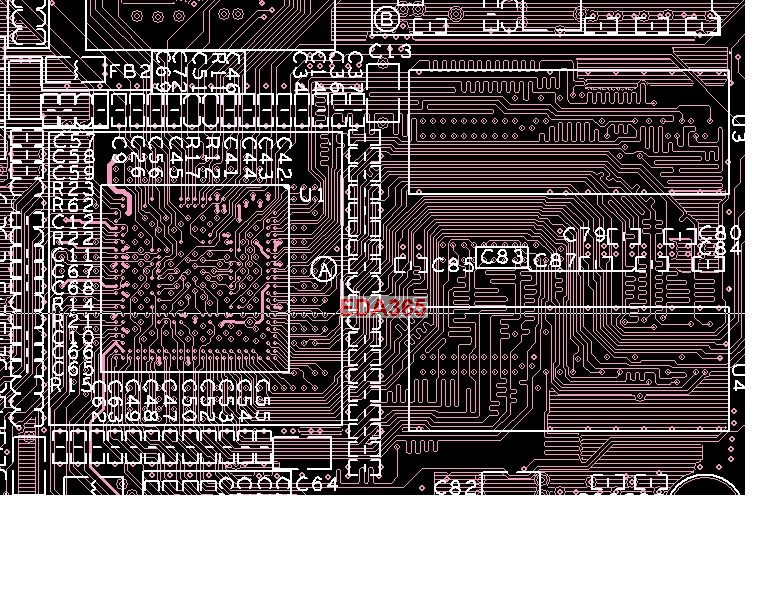

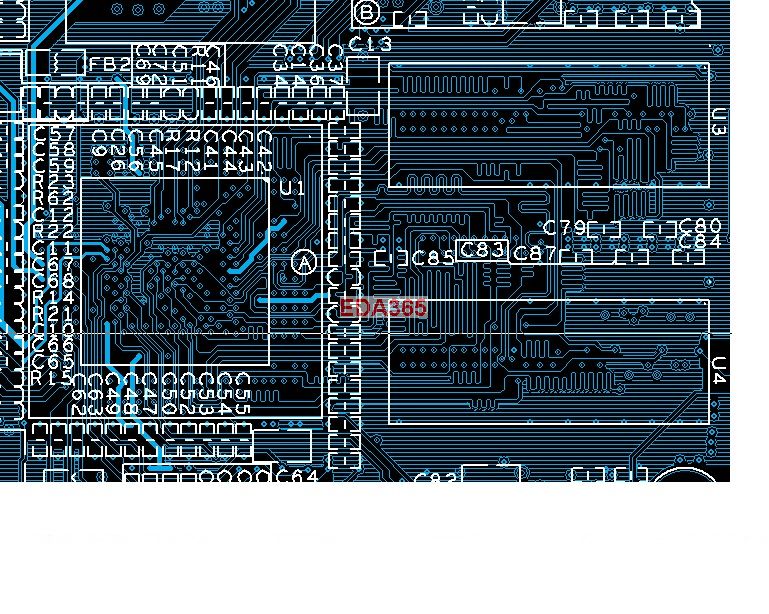

把ddr部分截个图出来

will大哥:

你说你在内信号层上,远离走线的四周铺铜,应该是为了给相邻信号层提供回流平面,使信号更好的回流。

那会不会出现这种情况:

假如层叠为sig1——sig2——GND。你在sig1层远离信号的四周铺铜。sig2信号本来已有回流层GND了,增加了sig1的铜皮之后,使sig2信号相邻的上下两层均有铜皮,会不会改变sig2层信号的阻抗,造成信号失配,恶化了sig2信号?

top

sig1

sig3

层叠顺序为top——sig1——GND——VCC——sig2——GND——sig3——bottom.

其中,gnd均完整。VCC割裂。

且,各个内信号层都做了铺地处理,不知是否是该原因影响。

数据信号分4组,【DQ0-7、DQM0、DQS0】、【DQ8-15、DQM1、DQS1】等等,同一组内的信号也没有完全在相同信号层里走,但是个人感觉应该问题不大。

数据信号,地址控制信号,clk和clkn全部等长+-25mil.

现象是:小文件能下进去,NK不行。基本可以确定问题出在DDR上。

检查下你各层信号的阻抗是否连续,另外提醒下如果信号线周围铺铜,会降低此信号线的阻抗

你控制阻抗了么,表层铺铜对阻抗的影响挺大的

top——sig1 之间的串扰貌似影响到你的ddr了!

个人看法:叠层不好,top层的高速走线没有参考平面,会和sig1串扰,如果内电层一定要三个走线层建议叠层为:

top-vcc-sig1-gnd-sig2-sig3-gnd-bottom

并且sig2和sig3走线十字交叉。

没有经过任何阻抗控制,因为要控制阻抗的话,需要通过和PCB厂家协商,更改线宽和线距的。

目前线宽3mil,改大的话走线就有问题了。

另外,你说表层铺铜对阻抗影响大,其实是影响第二层的信号阻抗吧?因为这样的话,第二层就有两个信号回流了。

就像我上面提的问题:

假如层叠为sig1——sig2——GND。你在sig1层远离信号的四周铺铜。sig2信号本来已有回流层GND了,增加了sig1的铜皮之后,使sig2信号相邻的上下两层均有铜皮,会不会改变sig2层信号的阻抗,造成信号失配?

但是,一般情况下,表层是要求铺铜的,这样可以减小电路板对外的辐射,那怎么解决表层铺铜导致的阻抗失配的矛盾呢?

多谢指教!

你说的对,之前没有考虑过top的回流问题的。

因为,原则上表层是不允许走线的,并且铺铜防止对外辐射。

没控制阻抗,3mil的线。建议你算下阻抗,现在阻抗是多少,一般这个在50-60欧姆没什么问题,如果偏离过大。你懂得

我看看发给pads的layout给你看看,不是layout的很好,但可以参考,那是我几年前的作品。

仿过没?

哇 那真是太好了!有个对比参考心里就有底多了!

那怎么发呢?发文件还是截图?