晶体GND 与 芯片GND 需不需要隔离 的问题,向大家请教

时间:10-02

整理:3721RD

点击:

大家好!

很多芯片都需外接一个石英晶体,我看到大部分的设计都是石英晶体正下方的GND与芯片的GND是隔离开的

但最近使用的Marvell的一个芯片,在Layout Guide里要求将保持石英晶体的GND与芯片的GND相同,不太理解

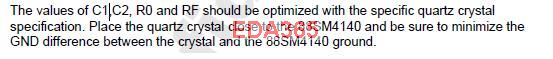

如下图:

请大家帮忙分析一下,晶体的GND和芯片的GND到低应该是哪种处理方式

多谢大家了

很多芯片都需外接一个石英晶体,我看到大部分的设计都是石英晶体正下方的GND与芯片的GND是隔离开的

但最近使用的Marvell的一个芯片,在Layout Guide里要求将保持石英晶体的GND与芯片的GND相同,不太理解

如下图:

请大家帮忙分析一下,晶体的GND和芯片的GND到低应该是哪种处理方式

多谢大家了

求高手哦

不是高手,发表如下看法:

大部分的设计都是石英晶体正下方的GND与芯片的GND是隔离开的----------貌似没听说过要这样处理。

我的理解是,晶体的地和芯片GND尽量短,有高频低阻抗路径,利于EMC。 另外是晶体地的接法似乎和晶体负载的寄生电容有关。

有高频低阻抗路径,请问这个是什么意思?烦请解释一下和EMC的关系

多谢了

在高频信号走线的时候,信号回流是选择低阻抗路径回流的。高频信号线正下方(参考平面)的阻抗为低阻抗,故回流路径是沿着信号线方向的反方向。