arm的stackup设计讨论

时间:10-02

整理:3721RD

点击:

现在做一块arm(PXA310)的板子,里面有要求比较多的阻抗控制,DDR, USB, bluetooth,还有一根天线

8层板,top/gnd/in1/vcc/gnd/in2/vcc1/bottom(个人想法,欢迎拍砖,当然也是参考比较典型的8层stackup)

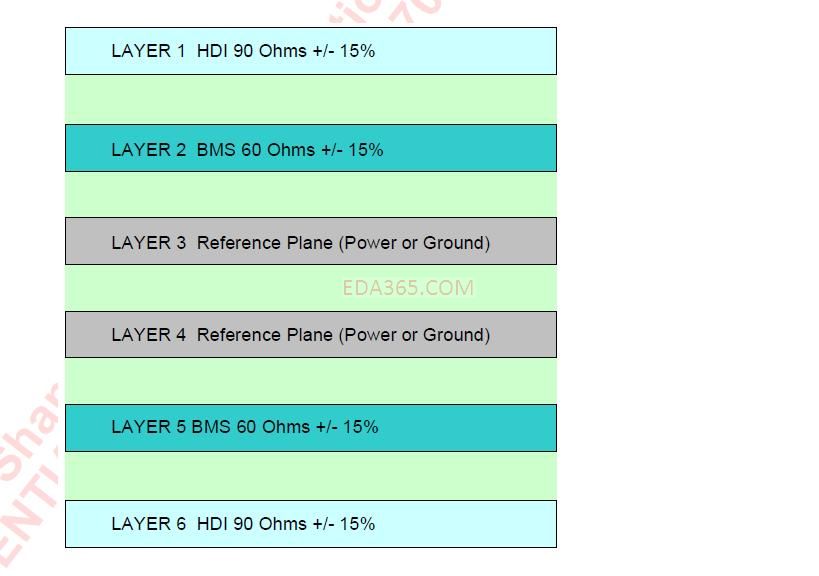

Guideline要求DDR的microstrip 阻抗控制在90 ohm, stripline阻抗控制在60 ohm,给出的线宽为3/4,姑且不去讨论制造工艺,一条net表层和内层的阻抗不一致肯定是不允许的,是我理解错误,还是guideline有问题呢,下面是guideline的stackup,注意是6层板的,表层的线都没有参考层面了,如何做阻抗控制,有图为证

现在认为guideline是不靠谱的,需要自己做一个stackup,综合USB差分阻抗90 Ohm,(单线也就大概40多吧),DDR的不靠谱的阻抗控制,应该如何设计stackup呢。以前没有做过类似工作,请教一下做stackup的基本流程,或者是一个大致的思路,具体的计算我再慢慢来。

电源阻抗有计算方法吗,还是说依靠经验做完了再做仿真没问题就OK

8层板,top/gnd/in1/vcc/gnd/in2/vcc1/bottom(个人想法,欢迎拍砖,当然也是参考比较典型的8层stackup)

Guideline要求DDR的microstrip 阻抗控制在90 ohm, stripline阻抗控制在60 ohm,给出的线宽为3/4,姑且不去讨论制造工艺,一条net表层和内层的阻抗不一致肯定是不允许的,是我理解错误,还是guideline有问题呢,下面是guideline的stackup,注意是6层板的,表层的线都没有参考层面了,如何做阻抗控制,有图为证

现在认为guideline是不靠谱的,需要自己做一个stackup,综合USB差分阻抗90 Ohm,(单线也就大概40多吧),DDR的不靠谱的阻抗控制,应该如何设计stackup呢。以前没有做过类似工作,请教一下做stackup的基本流程,或者是一个大致的思路,具体的计算我再慢慢来。

电源阻抗有计算方法吗,还是说依靠经验做完了再做仿真没问题就OK

顶起,大家看下

确实不靠谱

DDDDDDDDDDDDDDDDDD

layer1参考layer3

有图有真相

8层板,top/gnd/in1/vcc/gnd/in2/vcc1/bottom

这个为什么不设置成:top/gnd/in1/vcc/vcc1/in2/gnd1/bottom?

这样子电源与地相隔太远,电源阻抗比较大,无论哪一层做主电源层都很有问题。我的想法是VCC1的主要处理一些很难处理的电源,很多还是留给地,然后in2和bottom走一些不是很重要的线,重要的线下面再加上GND