CADANCE16.2-SI-振铃我接受,但怎有如此大的过冲?

时间:10-02

整理:3721RD

点击:

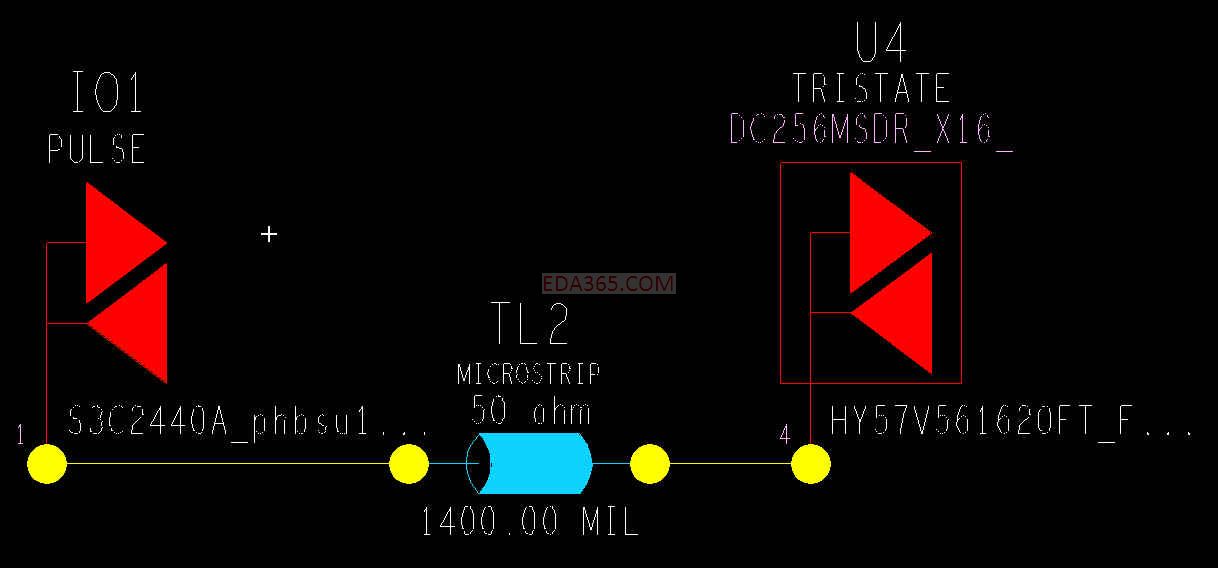

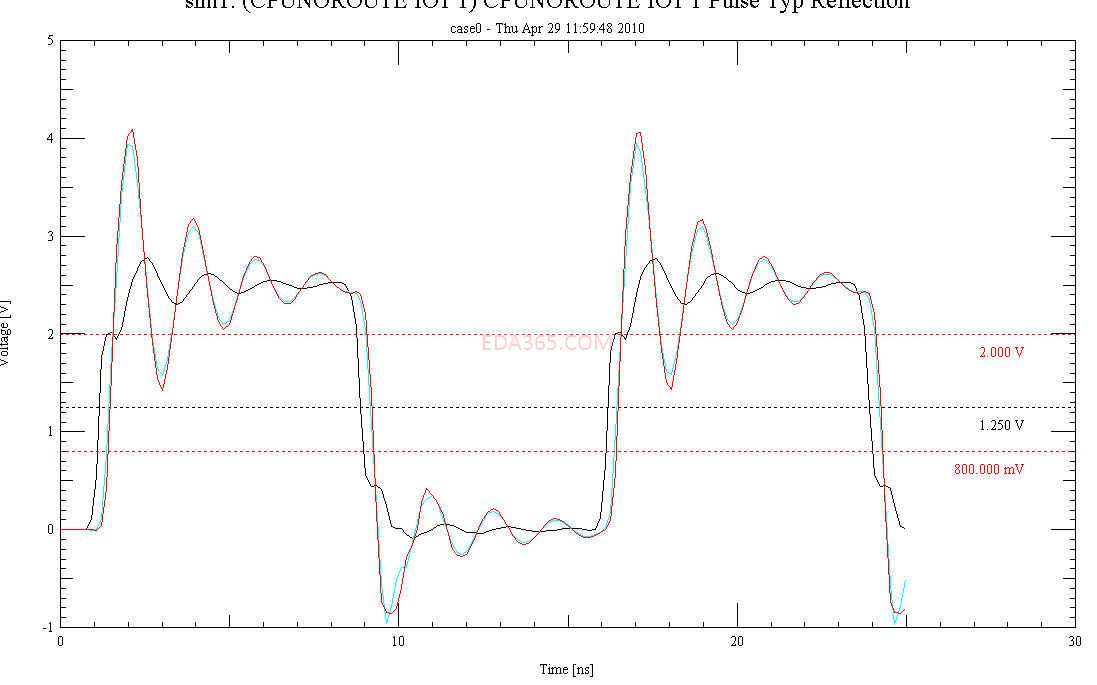

如上图,昨天做了S3C2440挂三个接收端的SI仿真,发现信号过冲很严重,于是简化了结构,点对点的仿真只带RAM发现情况依然存在,而且在接收端最严重。

请问是不是我哪里出了问题,模型问题我基本排除了,因为我手动用软件自带的defaultIO跑也是这个情况...

应该是出现过驱,现在如果把中间的传输线阻抗调整至20ohm就能很好的减少反射

信号的端口不都是50ohm的特征阻抗么,怎么调成20走线阻抗却反射小了...

迷惑 ~~~

望解答

公司封了附件看不到图。

你加了源端匹配么?根据你的描述,这个driver的源端阻抗显然只有20Ohm,需要33Ohm的source termination

未理解反射的原理怎么能仅靠仿真波形决定设计的优劣?

这个........

“应该是出现过驱,现在如果把中间的传输线阻抗调整至20ohm就能很好的减少反射”

已经考虑到是否阻抗匹配产生反射了,所以才会调传输线阻抗

但数据I/O口要挂三个接收端,考虑到驱动能力的影响没有加端接匹配

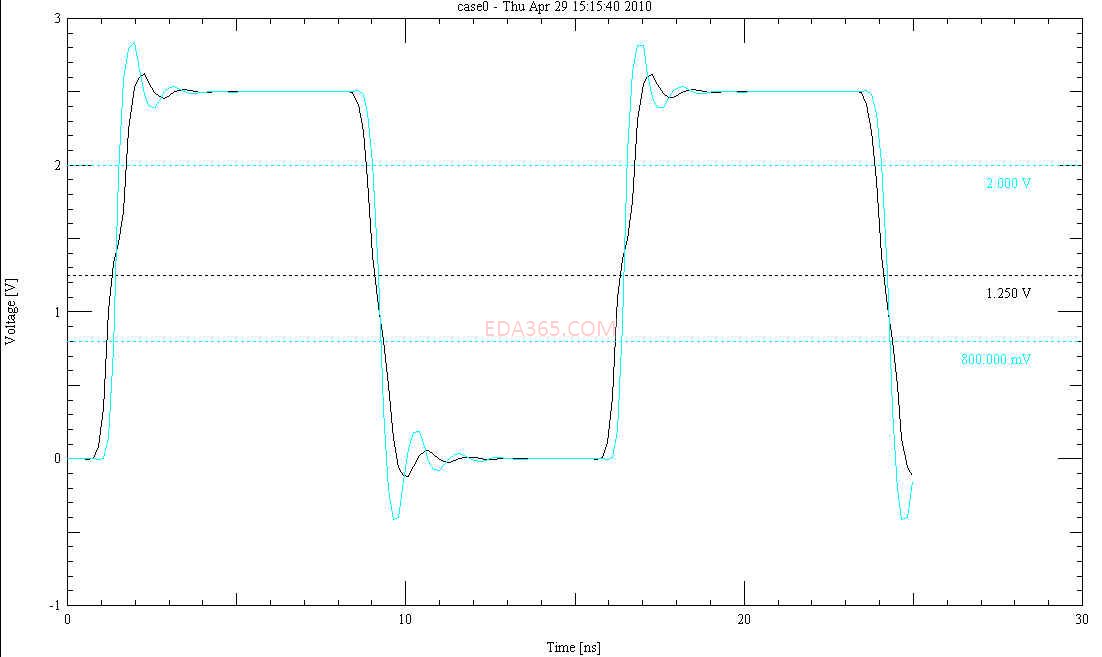

其实最后问题已经解决,是我山寨ibis模型问题,它把所有的data口模型定义换错了,昨天只关注接收端了

源端一直默认正确的......浪费时间啊