刚刚做了一个PCB,但是测试的时候增益很大

想了一下,地的噪声很大,以前没有遇到过这样的问题,如果给我的感觉地就是垃圾站,什么信号到底里面都会被排除,如一些高频噪声,会通过电感排到地上,可是我可以保证PCB,的地面积很大,几乎用了4.5层来铺,两层地层,不肯出现地不完整,而且模拟地和数字地分开,通过电感连接,可是噪声不仅在数字地上面有,模拟地上面也有,希望有那个朋友指点一下,找出原因,

你的噪声应该是电源噪声传导所致,跟地平面大小没有关系,应该是FPGA的电源设计不合理导致。

非常关注此贴!

但是刚才有测试了一下,FPGA在测试其他程序的时候,地的噪声也没什么大起大落,但是在调用FPGA内部时钟管理的时候,在122.88M的时候,左右会有一个30DBM的噪声,现在一直没有发现到底是哪里出错,而且也不知道怎么改版,不过谢谢两位的关心,请帮我分析一下,一开始我以为是DGND地层有阻抗所致,倒是想一想也没什么道理,后来想到AGND也有噪声就想办法用电感滤波,可是和没有一样,从而考虑到可能不是高频噪声,用的是1.2UH的电磁珠,现在正是不知道如何去调,没什么头绪,如果像ALLEN小编说的我们应该如何去做,才能测出错误的原因

能把你测试地平面的方法说明一下吗,你测试地平面,那么参考点连接在什么地方?

FPAG的内部时钟管理:你看看对应FPGA的电源设置有什么不妥之处,就是给时钟模块供电的电源怎么样?

你在调试单板的时候,这个单板的地,是否会接到实验室的公共地排上?

在布局上,PFGA是否出现跨在模拟地和数字地的中间交接处?

测试的方法是将频谱仪器,加到地上面,发现地上面加了很多杂波,发现 应该实在50M左右的波形,我们用得电源已经比较过了,应该是和原来的同样功能板子比较没差什么,再调试的过程中没有用到公共地,FPGA都是在数字地上面的,但是给我的感觉应该不是地的问题,但是有个老板说是时钟芯片和BGA距离太近,导致噪声把时钟感染了,带入整个PCB内部,但是我感觉这种解释我太赞同,因为对于频率并不太高的板子,出现这种情况,很难,因为最高频率才122.88M,如果是1G我也就认了,可是噪声也不高

会不会是122.88/2=61MHz的噪声?

因为这是信号最快switch的频率。

最主要是找到噪声来源,呵呵

加一些特征频率在50MHz的电容试试吧~

还有一点我忘记说了,就是用示波器看,是没有噪声的,只有用频谱观察才有,现在原因找不出来,却让我改版,我都不知道怎么改了,真是头疼啊

给FPGA和时钟芯片的电源加上LC滤波器,给时钟信号加上匹配电阻,再试试。

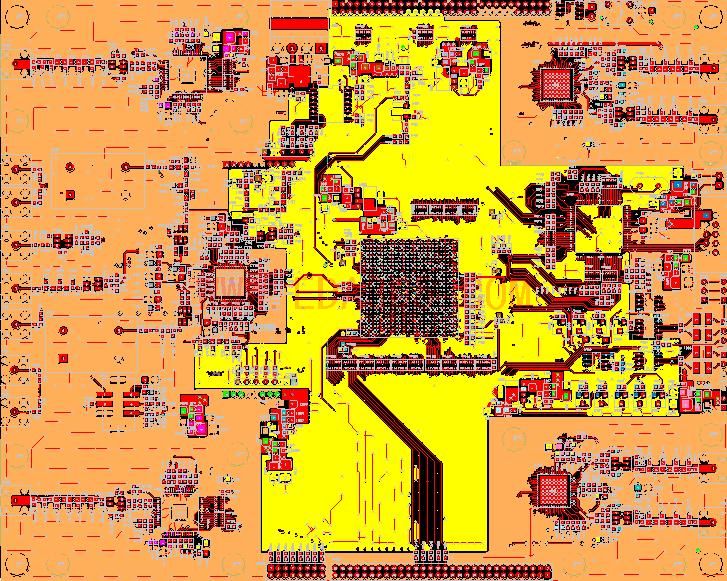

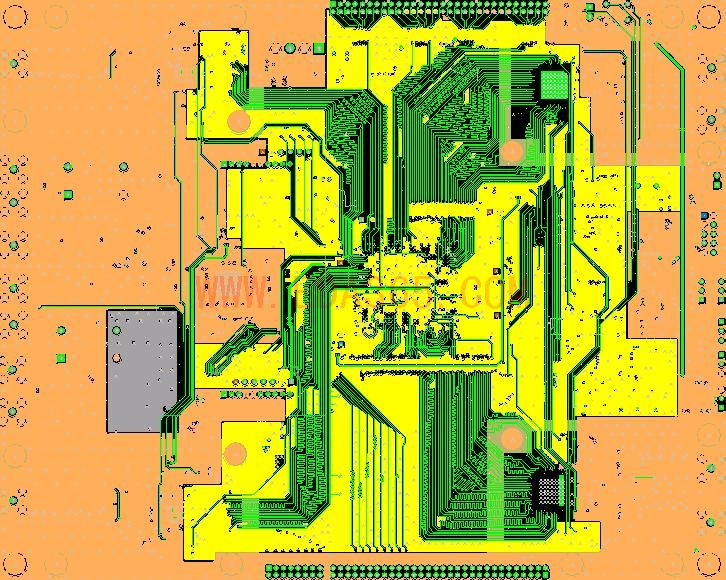

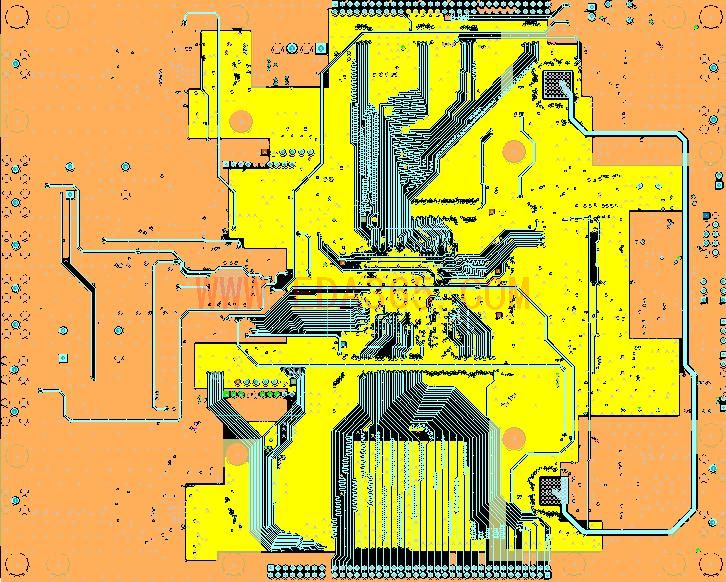

这些我们都加过,不过已经确定重新改版了,我就没事的时候调一下,我把我画的PCB贴出来,让大家看看有没有什么毛病,还有就是大家以后别范同样的错误

分别是顶层,信号1层,信号2层,和地层,

叠层为TOP-gnd-sig1-pow-gnd-sig2-pow-bottom

晕死,连上了,走线不一样的是不同层次的,且,黄色为数字地,棕色为模拟地,左中为时钟芯片,正中间为FPGA芯片

这个层叠,这个布线,和这个结果还是比较符合的.

没有针对叠层和上图的详细解释么?