画板碰到问题,请诸位高手指教

1:关于电源层,采用2电源层(第二层GND,第五层PWR),地层整个是一个,关于PWR,2440有两种供电电压:3.3V,1.2V(1.3V 400MHz)。

根据我查的资料,和现有的其他电路图,由于SDRAM和NAND都是3.3V供电,所以在整个PCB板上只有CPU下面的地方是1.2V的PWR层,其他地方都是3.3V,CPU上的3.3V电源是通过导线引出到3.3V的铜区然后过孔连接,这样做是否合理?

有的资料上说高速信号线不能跨越电源层的分割区,这一说法我认为是防止电流回路绕过分割从而加大串扰,我的PCB的第二层是一个完整的大地,从CPU上引出的SDRAM的时钟线,数据线,地址线如果都是在第一层和第三层,是不是电流回路就会以第二层的大地为参考而不会去绕电源层的分割,即使是在底层或者第四层,只要CPU和SDRAM的VSS都与地层相连,是不是回路仍然会从地层走,也就是说可以忽略PWR的分割区?

两个不同电压的分割区要多宽才合理?

分割的边界离CPU边界距离多少比较合适?

要不要跨接电容?

2:关于SDRAM的数据线,地址线,CLK,控制线

SDRAM的CLK是否一定要比ADDR,DATA,控制线长哪?

资料上说调整走线的长度是为了满足时序的要求,怎么理解满足时序?是不是将CPU发出的各个信号的延迟调整到时钟到达时都有效,并且数据返回到CPU时CPU不会读错数据(不会读到下一个周期的数据)?

对于数据线和地址线很多资料上说要分别等长,或者误差小于50mil,可是我计算使用FR-4,介电常数4.5,100mil的延迟大约是0.18ns,是否可以认为100mil也可以了?

有的资料上写允许的延迟与时钟上升沿的时间有关,怎样知道由CPU的PLL产生的SCLK上升沿的时间,是否只能通过实验测得?

时钟线如果要比其他线都长,是否也能蛇形绕线?不能的话应该怎么走?

3:关于阻抗匹配:

看到很多设计上SCLK都在靠近CPU端串接一个22或者33Ohm的电阻,这一阻值是怎么估计出来的?是不是K4S561632上也能用22或33Ohm?

请各位高手指教,不胜感激

1.高频信号回流路径为低阻抗通路(相对于参考面)。电源和地作为参考面的概念来说是没有区别的。跨越分割面走线意味着阻抗不连续,back loop的加大(包围面积磁通量的变大)。电源分割的安规可以理解为两块不同net灌铜区的clearance。我一般使用20mil。这么我没有很明确概念,请他人指教。

2.首先你要理解什么是同步系统,同步系统的参考信号就是CLK,你要做的是依据实际情况,在确定CLK长度的前提下,进而决定control,address,data的长度。当然对于源同步系统,需要关注的是strobe同data的延时差

之所以考虑到沿率,是要确定特征长度,进而决定是否需要将board level routing看作transmission line。沿率一般在数据手册中会有,或者对应的ibis model中会有。

3.源端串接电阻实现阻抗匹配。

Ro+Rs=Z0

Ro驱动端输出阻抗

Rs串接电阻大小(就是你提到的那些22ohm之类的玩意)

Z0传输线特征阻抗

讲的不一定对,请他人扶正补充

第二层GND,第五层PWR: 建议 3层GND,5层PWR: 地平面和电源平面尽量靠近,3层是地,2层和4层做SDRAM等高速信号走线,基本满足;同时电源和地的距离相对近一些。

CPU上的3.3V电源是通过导线引出到3.3V的铜区然后过孔连接,这样做是否合理?:如果你做了电源分割,这也是没有办法的事情,关键就看你是否愿意用导线引出1.2V或是3.3V,你现在的做法是芯片的整个下面都是1.2V了,这要看1.2V几个pin,是否有必要做这么大的面积,如果是条形的是否能解决。PCB

我的PCB的第二层是一个完整的大地,从CPU上引出的SDRAM的时钟线,数据线,地址线如果都是在第一层和第三层:表层不要走高速线了,你的阻抗不好控制的。

关于时序什么的问题:你理解一下在数字电路中数据是怎么 发出 和 采集 回去的吗?

十分感谢二位的解答,真是不胜感激

我会看一下关于同步系统和数字电路方面的资料

另外这里还有一点疑惑

表层不要走高速线了,你的阻抗不好控制:如果不走在第一层,所有高速线就要通过至少两个过孔,这样会不会对信号质量有影响?

另外CLK是否可以走蛇形线哪?

对于百兆SDRAM来说,两个过孔并不会对最终的信号质量造成过大的影响。

但是必须明确一个概念,信号换层走线就意味着阻抗不连续,这就是为什么高速信号的布线尽可能避免打过孔的原因(貌似微带天线就是要避免过孔影响)。

随着信号频率的提高,过孔引入效应已经对信号质量造成不可接受的影响时,就要着重考虑过孔的寄生参数(建模,调整参数)。

蛇形线,貌似没有造成阻抗不连续,但事实是,工艺上对于蛇形线拐角的实现都是一种近似处理,并不能实现严格的宽度一致,那么随之而来的便是阻抗mismatch,拐角处的reflection等等。

蛇形线除了用来实现timing的控制,无其他正面作用。

你的clk如果没有特别需要,只要满足timing要求,没必要走蛇形线

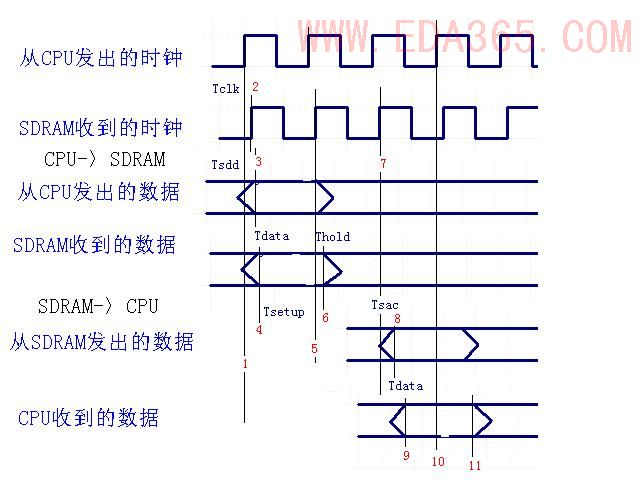

说明:

时钟周期:T = 10ns (100MHz)

Tclk:CLK在传输线上的延迟(线1到线2的时间)

Tsdd:CPU发出CLK到CPU输出DATA(由于地址和数据的延迟相同所以这里统称为DATA)的延迟,S3C2440上标注的是1~4(ns) (线1到线3的时间)

Tdata:DATA在传输线上的延迟(线3到线4的时间,线8到线9的时间)

Tsetup:时钟触发前所需要的建立时间(线4到线5的时间:SDRAM所需的建立时间(1.5ns),线9到线10的时间:CPU所需的建立时间(2ns))

Thold:时钟触发后所需要的数据保持时间(线5到线6的时间:SDRAM所需的保持时间(1ns),线10到线11的时间:CPU所需的保持时间(0ns))

Tsac:SDRAM收到时钟上升沿到输出数据的时间(线7到线8的时间)(max:6ns)

时序的要求:

对于CPUèSDRAM:满足Tsetup > SDRAM所需的建立时间 = 1.5ns;Thold > SDRAM所需的保持时间 = 1ns

即:T+Tclk-Tdata- Tsdd >Tsetup è 10+Tclk-Tdata-1>1.5è Tdata-Tclk<7.5

T – (T+Tclk-Tdata- Tsdd)>Thold è Tclk-Tdata-1 < 1 è Tclk < Tdata

对于SDRAMèCPU:满足Tsetup > CPU所需的建立时间 = 2ns;Thold >CPU所需的保持时间 = 0ns

即:T-Tclk-Tsac-Tdata>Tsetup è 10-Tclk-Tsac-Tdata >2è Tdata+Tclk<8 - Tsac

对于这一时序,我的理解就是要考虑Tclk < Tdata,其他的很容易满足

但是这里有个问题,在计算的时候都是假设数据的保持时间 = T,也就是 线4到线6的时间是10ns,如果数据的保持时间不是10ns对于以上的计算就不对了,至少计算CPUèSDRAM时,要满足Thold > SDRAM所需的保持时间 = 1ns的方程就不是这么列了,我在SDRAM上看到它的输出保持至少3ns,但是在2440的数据页上没有找到Output Hold time,所以这里才会假设线4到线6的时间是10ns,不然的话就是Tcpu_hold - Tclk + Tdata > Thold,假设CPU的hold time也是3ns,则Tclk<Tdata + 2;

不知这一问题如何解决?

Tcpu_hold: CPU时钟第二个上升沿到输出数据无效的延迟(图上是:线1之后的一个CPU时钟上升沿到CPU发出数据无效的时间)

以上都是我自己的理解,不知是否正确,请高手指点

[ 本帖最后由 nacassoce 于 2008-8-24 13:55 编辑 ]

我的个人看法:

1.设置第2,5层为地和电源是对的.不要整到第三层去,关于电源和地层是否应靠近点,在此案子的应用来看,得不偿失,因为第二层变成了微带线,辐射更大.当然,走线尽量走中间层,表层少走线.两三个过孔对2440的影响可忽略

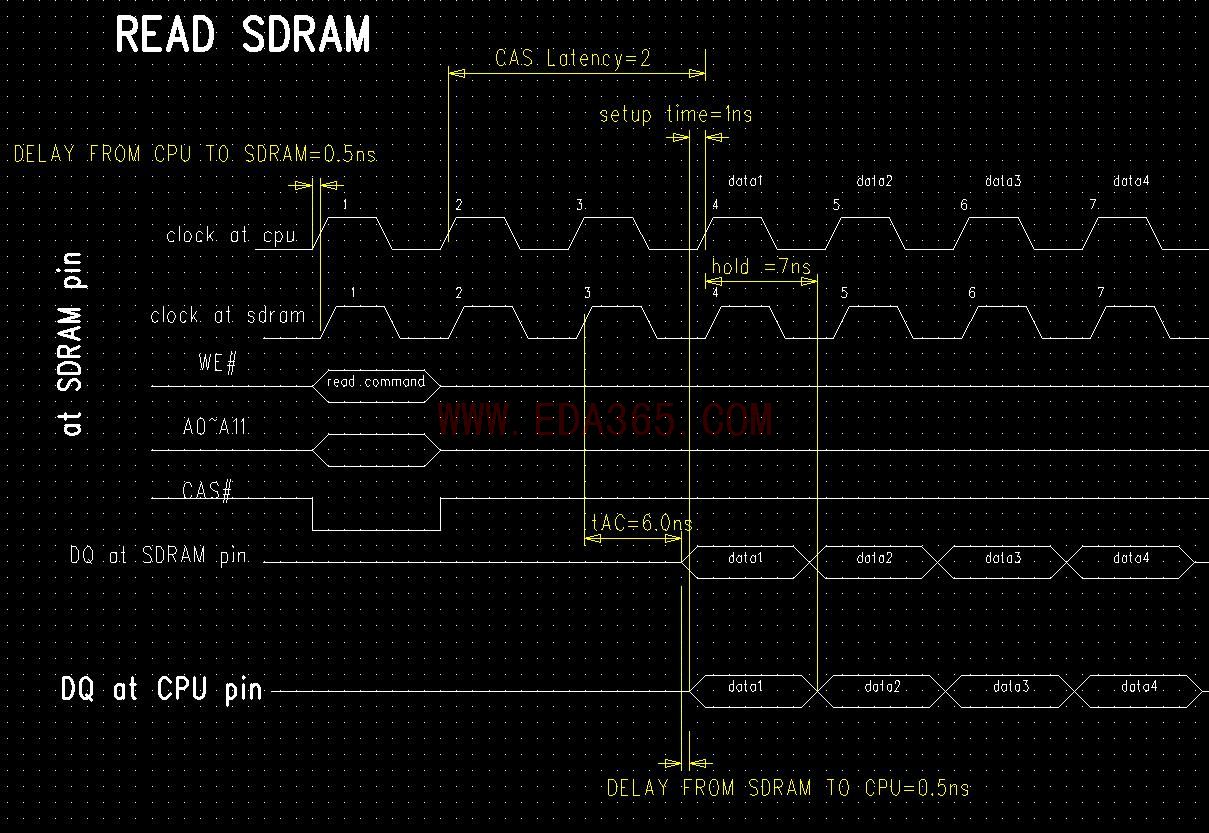

2.关于嵌入式系统的SDR SDRAM,这系统不同于其它的同步系统的是,它的读时序和写时序是极不对称的,并且CLK始终是由CPU产生的。主要着重考虑的是"读"建立时间.以一个125M,周期8ns为例简单估算一下。.内存最重要的参数是tAC,假设最大为6.0ns(绝大部分都在5。4~6。0之间)。

时序基准都以CPU的CPU上升沿的跳变时刻为0点。时钟从CPU到SDRAM的走线就用了0.5ns,然后第二个周期的tAC又花去了6.0ns,DQ才出现在SDRAM的PIN上,再过0.5ns之后才到CPU的引脚上。换言之,在下一个时钟上升沿到来之前的1ns数据都已经全部在CPU的DQ脚上准备好等待锁存。查看2440的SPEC,最小建立时间是2ns。时序裕量已经为负值了。要是跑100M,时钟周期10ns,还是绰绰有余的。至于HOLD的时间更宽裕得很。

实际在处理2440这类SDRAM的走线的时候,只要保证最长的一条DQ在CLK到来之前有足够的时间准备好就行了,等长也没太多必要,但是CLK一定要短。

坐上沙发学习,越来越感觉在这里真的学到不少东西。有种相见恨晚的感觉。呵呵

我了解了,十分感谢!

tAC-----DATA ACCESS TIME--------equal tco