高手帮忙,时序问题!

时间:10-02

整理:3721RD

点击:

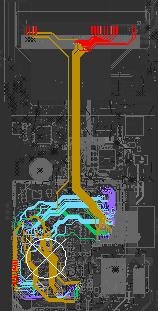

Data1~25 其中1~10 要到LCD,其余到Address 、CPU

现在问题是到的拉到 LCD的DATA很长,其余的很靠近RAM和CPU,

那现在等长怎么做,都要匹配到最长DATA 线的长度么?

图片如下:

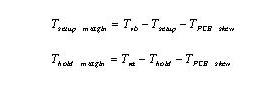

如果是源同步时序,使用的公式如下:

然后在器件资料里面查找相关的参数,代入公式即可求出。

不过由于各种器件资料给出的参数五花八门,经常你要理解这些参数,也理解这些公式才能灵活运用,算出结果。

当然在计算的时候,器件资料给的参数比较严格,这种使用公式的静态计算方法已经不能满足实际设计的需求。

因此很多公司都采用仿真分析的方法,其实也就是考虑的更加仔细,更加接近实际工作的参数进行计算。这种方法可以称做动态时序分析方法。

目前在一些时序特别紧张的接口中,还采用了紧时序,统计时序的分析方法,笔者认为这是以后时序分析发展的必然趋势。

上面这些只是简单介绍一下时序的一些方面,比较浅陋,请各位斧正!

现在问题是到的拉到 LCD的DATA很长,其余的很靠近RAM和CPU,

那现在等长怎么做,都要匹配到最长DATA 线的长度么?

图片如下:

大家有什么想法

都要匹配最长的么?

大家都怎么看的?

What type of the bus it is? you should read the timing requirement, then decide if length-matching is needed or not.

Data1~25

其中1~10 要到LCD,

其余到Address 、CPU

那么操作的时候,有时钟信号吗?

如果有时钟信号,LCD和CPU用的是同一个时钟信号吗?

如果是那么建议等长

如果不是。知道怎么做了吗?

同意楼上的,先看是同步时钟,还是异步得,不过按理CPU独立,很少和fpga用同一时钟,个人感觉

等长问题就是时序问题,而时序问题就需要进行时序分析才能知道。

分析过程大致如下:

确认是同步时序还是异步时序(一般数率高的都是同步时序),异步时序数率相对比较低,一般不用特别严格计算。

如果是同步时序,就要确认一下是公共时钟还是源同步。

如果公共时钟模式,使用的计算公式如下:

如果是源同步时序,使用的公式如下:

然后在器件资料里面查找相关的参数,代入公式即可求出。

不过由于各种器件资料给出的参数五花八门,经常你要理解这些参数,也理解这些公式才能灵活运用,算出结果。

当然在计算的时候,器件资料给的参数比较严格,这种使用公式的静态计算方法已经不能满足实际设计的需求。

因此很多公司都采用仿真分析的方法,其实也就是考虑的更加仔细,更加接近实际工作的参数进行计算。这种方法可以称做动态时序分析方法。

目前在一些时序特别紧张的接口中,还采用了紧时序,统计时序的分析方法,笔者认为这是以后时序分析发展的必然趋势。

上面这些只是简单介绍一下时序的一些方面,比较浅陋,请各位斧正!

不错,学习下.谢谢

问题被复杂化了吧

简单来说,CPU,RAM,ADDR这边做等长就可以了,往LCD那头不用去管它的时序,都不是一个系统了,真要有时序.问题,那是是因为LCD那边的D1~10的线长很多,所以反射会比D11~25小