晶体管开关读写SRAM存储器

时间:10-02

整理:3721RD

点击:

在四种常用晶体管开关电路(2种NMOS,2种PMOS)一文中,介绍了晶体管构成的开关电路。这里我们使用所述开关电路,搭建存储器编程开发环境,读写国产Lyontek的SRAM芯片:LY62L5128。国产的存储器好像比较少,支持一下。

一,LY62L5128 CMOS SRAM

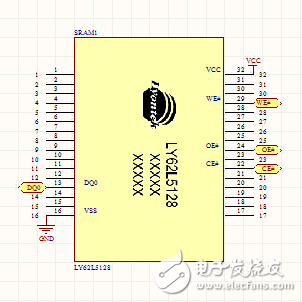

静态存储器(SRAM)是由静态存储单元和其读写控制电路组成的记忆体电路,对此的详细内容在四个晶体管搭建静态存储单元,加两个晶体管搭建写控制电路一文中。LY62L5128是一个CMOS SRAM。容量512KB(512K X 8 BIT)。因此有19位地址线(A0~A18)和8位数据线(称作DQ0~DQ7)。如图:

其中,引脚No.22(CE#)为“片选”(Chip Enable),引脚No.24(OE#)为“输出使能”(Output Enable),引脚No.29(WE#)为“写使能”(Write Enable)。全部是低电平有效。

VCC和VSS分别是参考电源和参考接地。其余27个引脚接地址线和数据线。

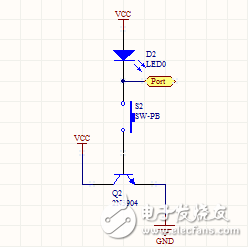

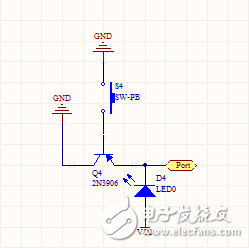

二,MOS 晶体管开关电路

回顾四种常用晶体管开关电路(2种NMOS,2种PMOS)一文中,1.2和2.2节所述NMOS和PMOS两种低使能开关电路,如图:

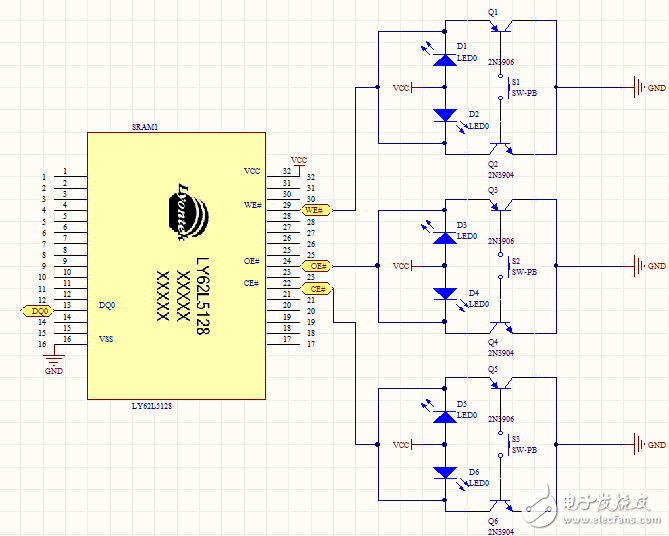

三,存储器编程开发环境

以NMOS开关电路为例,将其与LY62L5128连接,搭建存储器编程开发环境,如图:

按钮SW-PB:S1,S2,S3,分别通过MOS晶体管开关电路,连接到LY62L5128的控制引脚WE#,OE#,CE#。

因为MOS晶体管开关电路是低电平有效,LY62L5128的控制引脚也是低电平有效,所以按下相应开关即可“使能”相应控制引脚。2N3906和2N3904共同使用达到上拉功能。

四,LY62L5128 读写

简单起见这里示范仅读写一个BIT位:将地址线和数据线全部固定为一电平,对DQ0进行读写。

4.1 LY62L5128 写

根据LY62L5128写周期的波形图(请参考LY62L5128芯片手册),可以得到控制引脚电平的一个可行波形:

CE#低 -> WE#低 -> DQ0写 -> WE#高 -> CE#高

因此有对应按钮按键顺序:

S3按住 -> S1按住 -> DQ0写 -> S1弹起 -> S3弹起

DQ0可接参考接地或参考电源以写入0或1。

4.2 LY62L5128 读

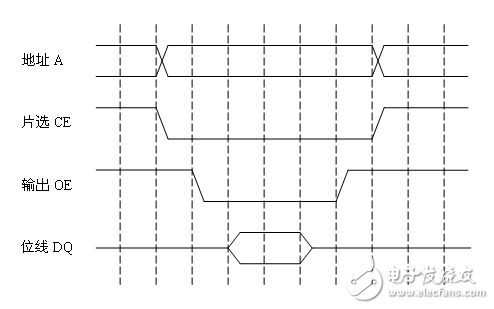

然后可以读取刚才写入的BIT位。根据读周期的波形图(请参考LY62L5128芯片手册),可以得到可行波形:

CE#低 -> OE#低 -> DQ0读 -> OE#高 -> CE#高

因此有对应按钮按键顺序:

S3按住 -> S2按住 -> DQ0读 -> S2弹起 -> S3弹起

DQ0可接一个LED以显示读取的0或1。

至此已经实现了在所搭建的存储器编程开发环境中读写一个BIT位的功能。

支持国产 Lyontek,再发一张实物图!

左下角纸上写的是管脚名称。面包板右侧三个开关分别是:WE,OE和CE。

OE(Output Enable)是 Lyontek 的输出使能引脚。输出时需要将OE置为低电平。同时因为静态存储器输出时会消耗一定的电量,因此读取完毕后应该将OE重置为高电平。这一点可以起到节能作用,适用于对电池使用效率要求特别高的应用。

写波形图。

读波形图。

更加详细的信息请参阅“LY62L5128”芯片手册。