四个晶体管搭建静态存储单元,加两个晶体管搭建写控制电路

时间:10-02

整理:3721RD

点击:

自己动手搭建电路可以发现许多有趣的东西。今天为大家带来的是“静态存储单元”及其“写控制电路”的搭建。

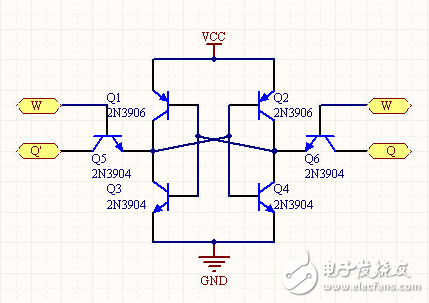

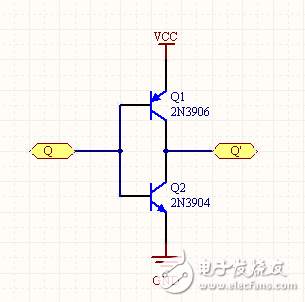

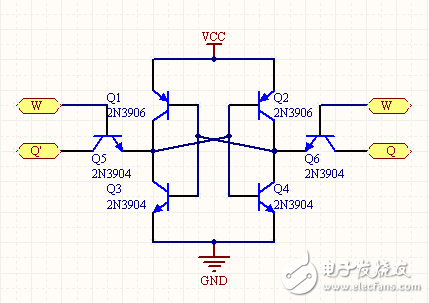

“静态存储单元”是构成“静态存储器”(SRAM)的最基本单元。其中每一个BIT存储在4个晶体管构成的2个交叉耦合的反相器中。而另外2个晶体管作为“写控制电路”的控制开关。

有趣的是,搭建这个电路需要严格对称。这表示面包板上左右两侧对应位置的走线距离必须完全一致,才能达到最好效果。

如图:

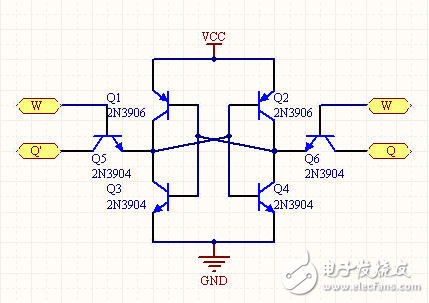

再来一张实物图:

下面的大面包板是“静态存储单元”,由晶体管Q1~4组成,上面的小面包板是“写控制电路”,由晶体管Q5、Q6组成。至此“静态存储单元”及其“写控制电路”论述完毕。

手绘和电路制作一样需要热情和细心。赠送一张手绘图片给大家!

图为《哪吒大闹东海之一》

走线方式都有要求。元器件更得精挑细选哦。

用同一长度线走线。减少交叉多用并行。没问题的。

杜邦线连线好像暂时不必考虑电容耦合和电感耦合。

电路图中的Q5,Q6的发射极是不是分别接在Q3,Q4的集电极上?

确实,忘了点了。就在这儿加以说明。感谢你!

这个应该是基极呀

基极和集电极都要接发射极。再画一张图:

原图已修订。

加油哦!

天行健!

哪吒大闹东海之一动画二

元宵节快乐!

花灯高挂红满天,

彩绸招张映红颜。

人迎春季春盛万,

春满人间人团圆。

小伙子,你不能发一些与题目无关的图呀,小心失足落入小黑屋.

可是我又没犯错,他为什么要关我呢。

那我发一个有关的。

小小鹿骑人

静态存储器单元与反相器的关系。

反相器由一个 NMOS 和一个 PMOS 组成。

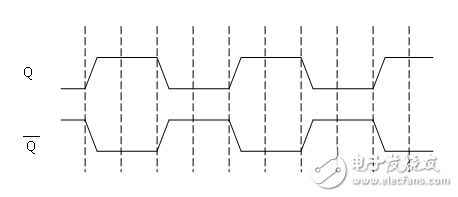

反向器波形图。

显然,2个反相器交叉耦合,就是前述的静态存储器单元了。

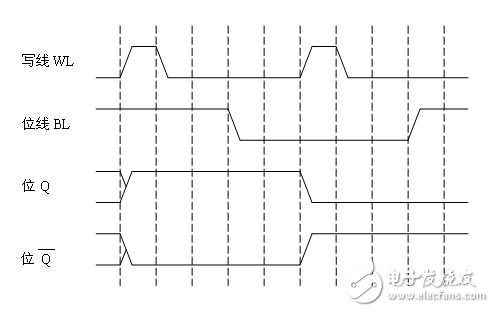

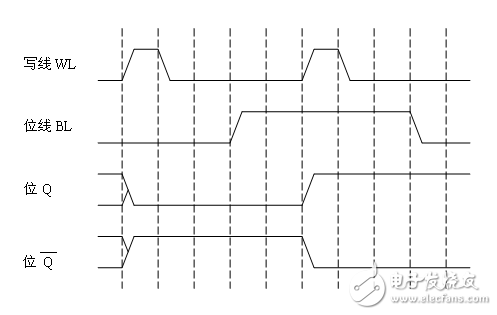

静态存储器单元波形图。

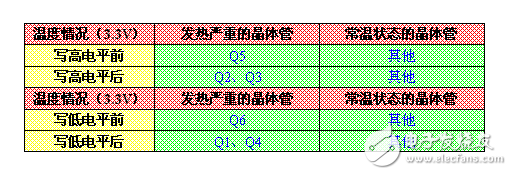

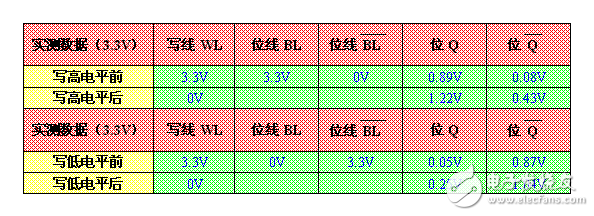

实测数据。

温度情况。