半导体巨头相继投入TSV 3D IC研发行列

DIGITIMES Research指出,随芯片集成度提高,除让芯片设计成本与时间随之增加外,芯片面积亦随芯片复杂度的提升而增加,在终端产品持续朝短小轻薄与节能省电方向发展下,更促使半导体厂商于制程微缩研发的持续投入。

根据摩尔定律(Moore’s Law)的预期,随芯片制程技术升级,芯片密度及产出数量每隔18个月将会成长1倍。然而,随晶圆代工制程跨入纳米级世代以来,摩尔定律进展速度放慢的声音就始终未曾停过。

事实上,从65纳米制程升级至45纳米制程,即长达24个月的时间,从45纳米制程升级至28纳米制程,更是历经33个月的时间,不仅远超过摩尔定律所预测的18个月,且制程升级所需时间也明显拉长。

如何能够More Moore及More than Moore,研发出兼顾高度集成与芯片效能,同时具经济效益的先进制程并导入量产,能够在相同制程下,提供更小IC面积,与更高度的集成,硅穿孔(Through Silicon Via;TSV)3D IC制程技术即成为半导体厂商重要技术研发方向。

也因此,包括三星电子(Samsung Electronics)、高通(Qualcomm)、美光(Micron)、台积电(TSMC)、日月光(ASE)等半导体大厂,皆先后投入TSV 3D IC的研发行列,并各自提出不同TSV 3D IC解决方案,就是希望未来能在TSV 3D IC市场争得一席之地。

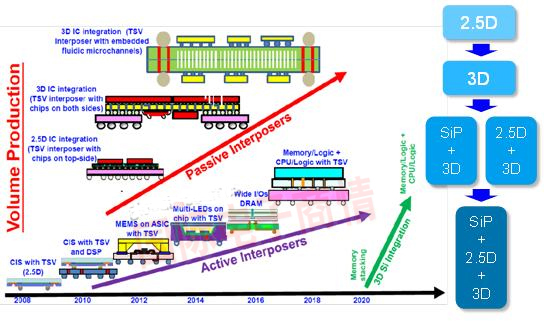

在终端产品持续朝向高度集成、小型化方向发展,亦将推动半导体技术更往更高集成度持续投入研发,因此,半导体集成技术将从TSV 2.5D IC技术进展至未来异质集成TSV 3D IC技术,甚至会进一步朝向TSV 3D加系统级封装(System in Package;SiP)或TSV 3D加TSV 2.5D ,乃至TSV 3D加SiP加TSV 2.5D更多元的异质集成封装决解方案发展。

- 大尺寸面板价格不涨反跌 市场供需失衡难落幕(07-29)

- 3D封装TSV技术仍面临三个难题(10-13)

- 全球MEMS代工排名 台积电营收激增200%(07-19)

- 导入TSV制程技术 模拟芯片迈向3D堆叠架构(09-17)

- 意法半导体(ST)推出全新运算放大器——精度更高且节省空间(11-19)

- 超级计算机要用上基于TSV的3D IC有多难(10-17)