详解LED PWM调光技术及设计注意点

PWM比"启动"接脚更快

即使是一个没有输出电容器的纯磁滞降压稳压器,都不足以应付某些PWM调光系统的要求,这些应用需要较高的PWM调光频率、高对比度度,也就是要求更快速的回转率和更短暂的延迟时间。与机械视觉辨识和工业检验系统搭配应用时,举例某些要求高性能的系统,包括液晶(LCD)面板和投影机的背光照明系统,在某些情况下,PWM调光频率必须被调高到可听频带以外的25kHz或更高的频带,随着整体的调光周期已缩短至几微秒内,包括传导延迟在内,LED电流的上升和下降时间总和必须缩短至奈秒内。

从一个没有输出电容器的快速降压稳压器着手,出现在输出电流开启和关闭的延迟,是来自集成电路本身的传导延迟和输出电感器的物理特性。若要达到真正高速的PWM调光,两个延迟都须被略过(By Pass)。要实现这个目标,最佳方法就是采用一个与LED并联的电源开关(图3)。当LED关闭时,驱动电流便会分流通过开关,作用就如同一个典型的N型金属氧化半导体场效晶体管(N-MOSFET),这时集成电路会继续运行,而电感器电流也会持续流动。该方法的最大缺点在于LED关闭时,即使期间的输出电压下降到与电流感测电压相同,仍会浪费功率。

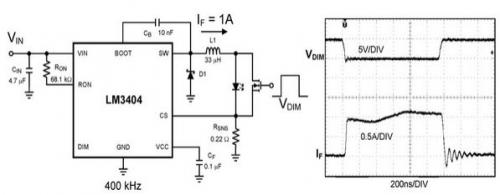

图3分路FET电路和其波形

利用分路场效应晶体管(FET)来进行调光会导致输出电压出现较为急剧的移位,这使得集成电路的控制回路必须作出响应,以尝试维持输出电流的稳定。正如同逻辑接脚调光般,控制回路愈快表示响应愈好,而采用磁滞控制的降压稳压器则可提供最佳的回应。

利用升压和降压/升压实现快速的PWM调光

无论是升压稳压器或任何类型的降压/升压拓扑都不太适合用在PWM调光。在开始设计的时候,会发觉两者在连续导通模式(CCM)下都会展现一个右半平面零点(Right-half Plane Zero)限制,这将无法达到频率稳压器所需的高控制回路带宽要求。此外,右半平面零点的时域效应还会使系统难以磁滞方式去控制升压或降压/升压电路;另一个使情况变得更为复杂的因素是升压稳压器不能容忍输出电压下降到输入电压以下,这种情况会导致在输入端产生短路,使得并列FET调光无法实行。另外,在各类的降压/升压拓扑技术中,并列FET调光仍然窒碍难行或极难使用,主因在于它需要输出电容器(SEPIC、降压/升压和返驰式),又或在输出短路时会出现无法控制的输入电感器电流(Cuk和Zeta)。

假如真的需要一个快速的PWM调光,最佳的解决方案是采用两级系统,并以降压稳压器作为第二级LED驱动级。不过,若尺寸空间和成本都不容许,退而求其次的最佳选择便是图4中的串行开关。

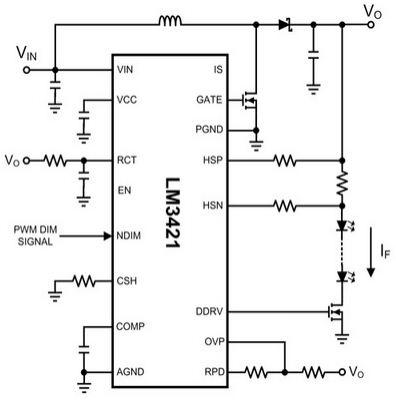

图4采用串行调光开关的升压稳压器

虽然LED电流可在瞬间关闭,但须仔细考虑系统的响应,这种开放电路其实可看成一个快速的极端卸除瞬时,它还会中断回馈回路并导致稳压器的输出电压无止境上升。因此,须要在输出和/或误差放大器加入箝位电路,以预防超载电压所造成的损害,但由于这些箝位电路难以用外部电路的方式实现,也就是说串行式FET调光必须配合专用升压与降压/升压LED驱动器集成电路才可使用。

要有效控制LED光源,必须在开始时的设计过程就加倍小心,光源愈是精密,须要采用PWM调光的机会就愈大,而系统设计人员也必须谨慎考虑有关LED驱动器的拓扑结构问题。降压稳压器对PWM调光有很多优点,设计人员必须慎重考虑输入电压和LED的排列位置。假如调光频率要求更高,回转率便要更快,如此可更轻易在设计过程的初期改用降压稳压器来实行。

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 改善 PWM 电源控制器低负载运行的缓冲放大器和 LED(01-16)

- 负输出罗氏变换器实用性剖析(01-09)

- 一种新型ZCS-PWM Buck变换器研究(02-20)

- PWM技术实现方法综述(02-19)

- 基于HPWM技术的大功率正弦超声波逆变电源(02-26)