填补网络 SoC 设计前端与后端验证的差距

时间:09-19

来源:3721RD

点击:

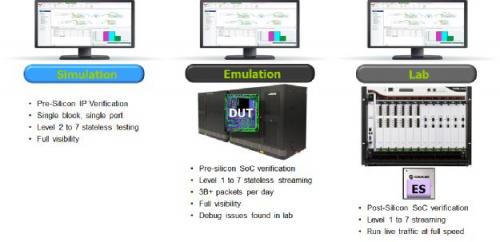

图 8.Mentor/IXIA 集成消除了从软件仿真到硬件加速仿真再到实验室的验证环境中的所有差距(信息来源:Mentor Graphics & IXIA)

通过使用该系统,网络设计团队能在软件仿真、硬件加速仿真和实验室中运行相同的测试。它支持高性能,并可为前端验证提供调试优势。实验室中未发现的错误可在硬件加速仿真中通过与实验室相同的测试环境进行追踪。其中包括 PCIe、以太网和可能位于网络交换机上的其他 VirtuaLAB 解决方案。测试整个产品中发现的错误,包括硬件和软件,可在硬件加速仿真中立即再现,但若不使用由 IXIA 和 Mentor Graphics 共同开发的这些最先进的虚拟化技术,这种硬件加速仿真则可能需要数周才能复制。

最终,通过使用后端软件开发工具包 (SDK) 和测试环境,可以实现真正的"提前"前端验证功能。消除复杂网络 SoC 开发风险不再是遥远的目标;如今,所有设计团队都可以实现。

- 无线自组织网络测试平台设计与实现(08-18)

- 利用RLDRAM II存储器提高网络设备性能(01-06)

- 基于SIP协议的语音网关开发设计(01-06)

- 解密未来通信:融合与统一——纵观第七届中国网络大会(01-05)

- 中兴通讯中小企业网解决方案(01-08)

- 基于蓝牙模块ROK 101 007/1的小区安全监控系统设计(01-08)