实时以太网EtherCAT从站的硬件系统设计

本设计中,物理通信端口使用的是端口0与端口1,且使用能传输100 m的MII类型,则有如下配置信息:P_MODE[0:1]下拉决定端口0与端口1被使能用,而P_CONFIG[0:1]上拉表示端口0与端口1使用MII类型。本文物理芯片选用的是KSZ8721,其电路连接图如图4所示。

2.3过程数据接口

从站控制芯片ET1100的应用数据接口又称为过程数据接口,简称为PDI.PDI是微处理器与ET1100进行数据交换的接口,是底层接口电路,为上层复杂的应用协议提供硬件基础。ET1100的PDI接口可分为SPI接口、微处理器接口和数字量I/O接口,这三种接口的实现通过PDI控制寄存器0x140取不同的值来实现。而ET1100中控制寄存器的值是上电时自动加载EEPROM中用户配置的数据,并且ET1100提供一专用引脚来表征此配置信息是否被正确加载。当此引脚信号为高电平时,表示配置信息被正确加载,此时端口才会被激活。本设计中三种接口方式皆可以使用,但是SPI接口具有接线少、使用方便、传输速度快等优势,因而后续的测试实验中使用SPI接口与测试开发板进行连接。

图5 EtherCAT硬件接口实物图

综合以上信息,本文详细介绍了从站硬件整体框图、ET1100的物理通信端口、PDI接口以及外围芯片具体选型与使用,最终设计的具体电路的实物图如图5所示。

3 EtherCAT从站软件设计

EtherCAT从站的软件设计主要包括微处理器的软件设计和ET1100的软件设计。在本设计中,由于嵌入式主站的设计工作很复杂,所以本测试的主站由PC机担任,PC机通过倍福公司的TwinCAT软件实现主站功能,主要负责所有从站设备的工作状态以及管理主从站之间的数据通信。

ET1100的软件设计就是把配置好的与硬件相符的XML文件烧写到EEPROM中,最终实现主从站之间的通信。微处理器dsPIC30F6014A的软件设计通过操作ET1100实现应用层协议,其任务主要完成dsPIC30F6014A硬件的初始化、ET1100的初始化以及过程数据的处理等。

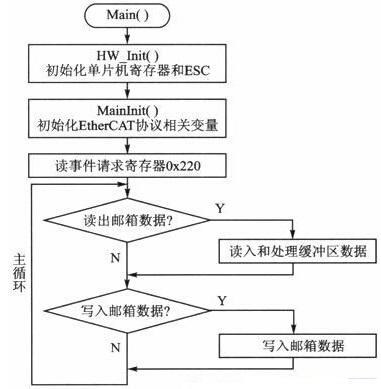

非周期性数据通信与周期性过程数据通信是EtherCAT网络中主从站之间数据交换的两种形式。周期性过程数据通信采用现场总线逻辑单元进行寻址,缓冲区可以被主从节点同时访问;非周期性数据通信采用邮箱方式进行,邮箱数据通信使用两个存储同步管理通道,通常主站到从站通信使用SM0,从站到主站通信使用SM1,它们可被配置成一个缓冲区方式,使用握手来避免数据溢出,只有把缓冲区数据写满后,另一端才能读取,并且只有当内存中的数据全部读出时,一端才能重新写入数据。本实验中,从站程序采用的是非周期性数据通信,并且采用的是查询方式,程序流程图如图6所示。

图6 从站程序总体流程图

4测验测试及分析

4.1 I/O开关量的实验测试与分析

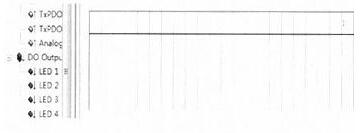

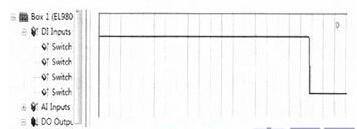

以设计的基于从站控制器ET1100的EtherCAT从站接口卡和Microchip公司的dsPICDEM1.1 Plus Development Board开发板构成从站设备,PC机凭借德国倍福公司开发的TwinCAT软件作为主站设备搭建实验平台。首先,打开TwinCAT软件中的System Manager功能,找到I/O Device,单击鼠标右键扫描设备,找到BOX设备,烧写XML配置文件到ET1100中,完成特定功能的配置,按照功能要求对从站接口板与开发板进行正确的连线。在TwinCAT软件以及开发板中编写测试程序,通过观察开发板上LED的明亮以及TwinCAT软件中的图示,来验证EtherCAT中主从站之间的通信是否成功。具体实验结果如图7~图10所示。

图7

图8

图9

图10

由图7、图8可知:主站TwinCAT软件中,写入开关量1(即高电平),从站实验平台中LED被点亮,验证了主站到从站数据传输的正确性。由图9与图10分析可得:对从站平台按下按键,输出低电子,上位机主站得到了从高电平到低电平的突变,从而从站到主站的数据传输的正确性得到验证。综上所述,主从站之间实现了双工通信,并且验证了所设计的从站接口卡的可行性。

4.2 EtherCAT从站的实时性能测试

以SOURCEFORGE上开源的SOEM(Simple Open EtherCAT Master)软件,基于嵌入式操作系统Linux的应用环境,以及本设计中的从站接口卡作为测试平台,对EtherCAT数据传输的实时性进行测试分析。在不同从站节点个数组建的网络下,采集实验数据,实验数据包括主站控制周期平均值、环运行时间。通过分析实验数据可知,本设计的从站接口卡达到了预定要求,实验数据如表1所列。

分析表中数据可以得出:在不同从站节点个数组建的网络下,周期是不变的(约为0.5 ms),这是由主站来控制的;环运行时间随着节点数的增加而成倍增加,每增加一个节点,环运行时间增加1μs,也就是报文经过