基于AES的网络加解密系统系统硬件图及完整源代码

口设计及其地址空间映射

该IP core所有信号都是同步的,时钟上升沿有效,具体接口信号设计如表2.1所示。

表2.1 IP core 接口信号

| 信号名称 | 信号位宽 | 信号方向 | 信号描述 |

| clk | 1 | in | 总线时钟 |

| reset | 1 | in | 同步复位信号 |

| writedata | 32 | in | 根据地址从数据总线上写入32位数据 |

| address | 5 | in | 地址信号,5位地址即可表示32个地址空间 |

| write | 1 | in | 写使能信号 |

| read | 1 | in | 读使能信号 |

| readdata | 32 | out | 根据地址从数据总线上读出32位数据 |

| waitrequest | 1 | out | 等待信号 |

| irq | 1 | out | 中断信号 |

根据表2.1可以看出所有的接口信号都是按照总线规范设计的,这样使本设计能够直接作为自定义组件集成到系统中使用。IP core的密钥、加/解密数据以及所有的控制信号都是通过32位数据总线传输的,为了使IP core能够识别,需设计出合理的地址空间映射,如表2.2所示。

表2.2:IP core地址空间映射

| 地址偏移量 | 名称 | 描述 |

| 0X00-0X07 | KEY | 初始密钥,为只写内存区 |

| 0X08-0X0B | DATA | 输入处理数据,为只写内存区 |

| 0X10-0X13 | RESULT | 处理结果数据,为只读内存区 |

| 0X14-0X1E |

| 保留 |

| 0X1F | CTRL | 控制状态字 |

表2.2中,控制寄存器CTRL控制着IP core的功能和轮询的状态,它是可读可写模式。本设计只用到4个字节的第0个字节,第1到第3个字节保留待用。控制寄存器CTRL各位的映射如表2.3所示。

表2.3 控制寄存器映射

| 偏移位 | 名称 | 描述 |

| 31-8 |

| 保留 |

| 7 | KEYVALID | 密钥有效位 |

| 6 | IRQENA | 中断使能端 |

| 5-2 |

| 保留 |

| 1 | DEC | 解密模式 |

| 0 | ENC | 加密模式 |

(2) 有限状态机控制模块

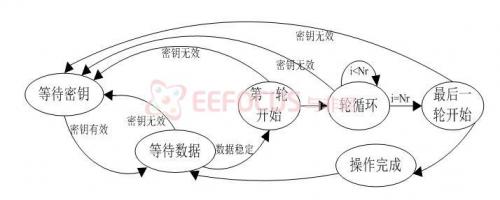

该IP core加/解密工作首先需要初始化一个密钥,密钥初始化完毕后就会启动密钥扩展模块,产生各个轮运算所需要的轮密钥,轮密钥产生完成后,传入需要操作的数据块,然后根据有限状态机的控制完成各轮加/解密,最后完成操作,加/解密有限状态机如图2.6所示。

图 2.6 加/解密有限状态机

3.2 软件设计部分

嵌入式系统的软件,用于协调各个子模块和数据的调用,是实现设计者思想的主要手段。软件模块主要包括AES组件相关程序与应用程序。

部分主要代码如下:

// AES头文件

#ifndef AES_H_

#define AES_H_

#define KEYWORDS 8

#define AES_BASEADDR 0x02902000

#define KEY_ADDR AES_BASEADDR+0x00

#define DATA_ADDR AES_BASEADDR+0x08

#define RESULT_ADDR AES_BASEADDR+0x10

#define AESCTRLWD AES_BASEADDR+0x1F

typedef struct{

volatile unsigned int* key;

volatile unsigned int* payload;

volatile unsigned int* result;

volatile unsigned int* control;

} aes_handle;

void aes_init(aes_handle* context);

void aes_setKey(aes_handle* context, unsigned int* key);

void aes_setPayload(aes_handle* context, unsigned int* payload);

void aes_setKeyvalid(aes_handle* context);

void aes_encrypt(aes_handle* context);

void aes_decrypt(aes_handle* context);

int aes_isBusy(aes_handle* context);

#endif /* AES_H_*/

// AES常用

MicroBlaze AES-128 FPGA 解密系统 IP核 相关文章:

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)