基于FPGA的高速多路视频数据采集系统

设计通过除法器控制Skip信号,将行像素计算器的输出值作为除法器的分子,分母为9,skip信号由除法器余数控制,当余数为0时Skip信号有效。采用这种方案将行像素点由720转换为640。

2.3 SOPC自定义FIFO接口

由于视频输入部分工作在27 MHz的时钟频率下,而NiosII软核CPU为了获取较高的系统处理能力,整个SOPC系统工作在100 MHz的时钟频率下。数据从外部进入SOPC系统的过程中由于时钟的不匹配,极易造成数据重复或丢失,而异步FIFO正是解决这个问题的关键。采用异步FI FO作为数据缓冲接口,低速时钟域接收来自视频解码模块的Raw Data图像数据,完成写FIFO操作;高速时钟域响应DMA控制器的读请求,由DMA控制器完成读FIFO操作。

多路视频数据存储接口模块通过SOPC的自定义外设实现,本设计针对多路视频数据采集,可根据每路视频数据的不同格式单独为每路视频数据定制存储接口。这种设计一方面降低了系统硬件结构的复杂度,另一方面保证每路数据独立并行传输,提高数据采集的效率。自定义外设接口遵循Avalon总线协议,根据发起数据操作的方式不同,分为Master和Slave两种,本系统的多路数据存储接口模块采用Salve模式。

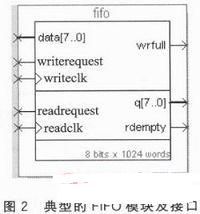

自定义存储接口模块以FIFO IP Core为核心,通过与Avalon总线协议匹配,接收NiosII处理器的控制信号。该模块利用QuartusII中Mega Wizard Plug-In Manager实例化FIFO IP Core,根据数据格式和系统资源综合考虑,FIFO的数据宽度为8位,FIFO深度为1024。在这里保留FI FO IP Core的读时钟信号readclk、读请求信号readrequest、8位读取数据接口q[7:0]、8位写入数据接口 data[7:0]、写时钟信号writec lk、写请求信号writerequest以及FIFO空状态信号rdempty。实例化后的FIFO模块如图2所示。

在SOPC自定义器件的配置过程中,根据我们所要实现的功能,FIFO的写入端应为SOPC系统的对外接口,FIFO的读取端应与Avalon总线挂接,并能被DMA控制模块读取。图3为实例化后FIFO模块作为自定义外设引入SOPC系统时的接口配置。

2.4 DMA控制器模块

DMA控制器负责将自定义FIFO接口中的数据搬移至存储区域,每路视频数据源对应一个FIFO接口,每个FIFO接口配有一个DMA通道,各路视频数据的解码、存储互不影响。SOPC系统所支持的DMA控制器IP Core传输模式有3种:

①存储器到存储器模式。这种情况下需要同时打开发送通道和接收通道,而且源地址和目标地址都是自增。

②存储器到外设模式。这种情况下只要打开发送通道,而且源地址自增,目标地址固定。

③外设到存储器模式。这种情况下只要打开接收通道,而且源地址固定,目标地址自增。

本系统设计中,DMA控制器工作任务是将自定义外设存储接口的数据搬移至SDRAM内存中,所以采用第3种DMA控制器工作模式,即从外设到存储器模式。这种工作模式下,源地址是自定义外设的地址,是一个固定地址。而目标地址是SDRAM存储器地址,需要地址自增,在数据传输过程中,由DMA控制器自动完成目标地址自增操作。SOPC系统中的DMA控制器IP Core配置中的DMA寄存器的宽度大小,决定了一次DMA传输所能传输的数据量大小。本设计所需搬移的数据量为一帧图像大小。

2.5 存储空间设计

本系统方案中根据开发板的资源,将多路采集的视频数据分别存储在两块SDRAM中,SOPC系统中两块SDRAM的基地址分别为SDRAM_0_BASE与SDRAM_1_BASE。一块SDRAM中存储的每路视频数据间隔RAM_PROTECT_SPACE的地址空间,DATA_SPACE定义了每路视频数据存储在SDRAM中的预留空间大小。由此可得第n路视频数据在SDRAM中的存储空间的地址。

起始地址:DATA_n_START_Addr=BASE_ADDRESS+RAM_PROTECT_SPACE。

结束地址:DATA_n_END_Addr=DATA_n_START_addr+DATA_SPACE。

3 系统软件设计

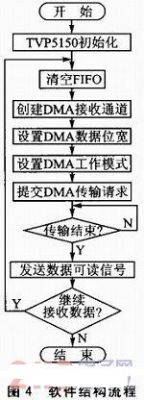

本方案软件部分主要为TVP5150芯片初始化、DMA控制器的配置等。软件结构流程如图4所示。

4 实验结果

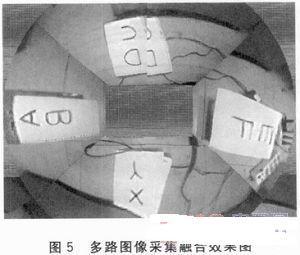

为检验高速多路视频数据采集系统的图像采集效果,系统外接4路摄像头同时采集图像数据,在实际视频数据采集过程中,多路视频图像显示连贯流畅。将存储在SDRAM中的图像数据读取后,通过后期融合算法,融合成环境平面图像,实际多路图像采集融合效果如图5所示。

结语

本文基于FPGA设计了一种高速多路视频数据采集系统,该系统通过外接视频扩展板连接多个视频摄像头,通过在FPGA内部构建视频解码模块,能够对每路视频数据并行解码,提高要求实时性的多路数据采集的效率,并可在不更改硬件设计的前提下对编码格式的数据采用不同的解码模块。SOPC系统的自定义FIFO接口能够高速缓存视频数据。通过DMA IP Core的使用,可

- Snell Advanced Media 选择金雅拓来保护对于知识产权的威胁(06-22)

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)