高带宽数字内容保护技术接收端的研究与设计

研究了高带宽数字内容保护技术的接收端设计。分析讨论了HDCP接收端的基本结构以及实现接收端的设计方法,其中包括数据加密、控制器、寄存器、I2C接口共4个子模块的设计。HDCP是一个内嵌在数字电视接口或高清晰度多媒体接口芯片中的IP核模块。将HDCP集成在DVI\HDMI接口芯片中,可以保证视频数据在视频设备间传输的合法性、保密性且不被窃取。

高清视频信号是一种典型的可以从一个系统传输到DVI\HDMI接口的信号。这些接口能保证传递的视频图像保持原本的质量,因此可以获得更多的终端用户,但对于企业来说,同时会出现更多没有经过授权和非法复制传输的风险。

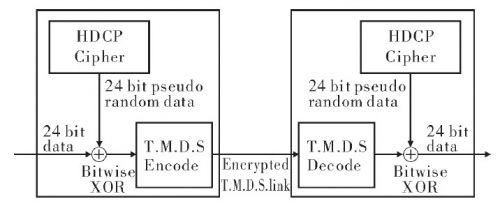

传统的知识版权保护技术仅仅能够保护已经存储在某种介质上的数据,但是高清视频信号仍然能够通过DVI\HDMI之类的数字接口进行传输,为了解决这个问题,HDCP就应运而生。HDCP是一个基于数据加密和授权验证的内容保护系统。图1描述了HDCP在数字视频信号的发射端和接收端系统中的角色。

图1 视频传输系统中的HDCP

为解决速度和功耗的问题,使用最小差分信号传输(TransitiON Minimized Differential Signaling,TMDS)来传输信号。在DVI和HDMI里都有一个为控制在发送端与接收端信息交换的通道,这个通道类似于显示器数据通道(Display Data Channel,DDC)。

1 HDCP接收端的结构

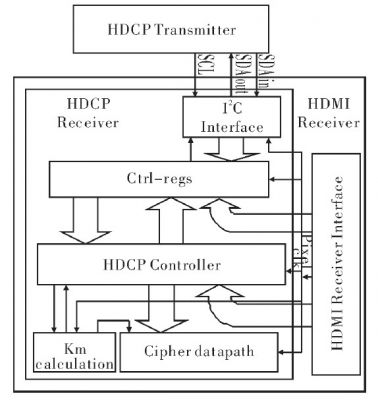

图2描述了HDCP接收端的基本结构。HDCP接收端有2个通信模块:HDCP发送端位于HDMI\DVI接收端芯片的外部;而接收端位于HDMI\DVI接收端芯片的内部。

图2 HDCP接收端的结构

HDCP发送端通过I2C总线发送授权认证信号给接收端。HDMI接收端接口通过HDCP控制寄存器的更新来发出操作指令,从而控制HDCP接收端的状态,以及提供必要的信息HDCP接收端知道工作在视频传输的阶段,从HDMI接口接收到解密信息并发送回去。

HDCP接收端由4个模块组成:I2C从机接口,控制寄存器,HDCP控制器以及数据加密机。应该注意图2描述的是HDCP接收端的工作环境,不能把它理解成HDCP发送端和HDMI接收端输入或输出信号的最终传输示意图。文中的最终目标是设计一个同时能够支持DVI和HDMI的HDCP接收端。

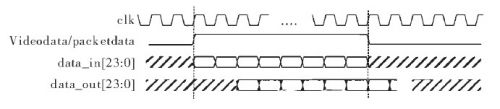

当打包数据或视频数据是逻辑高电平时,数据从HDMI输入到HDCP接收端的解密才有效。数据的输入与输出必须在2个时钟周期内完成。HD MI只有在这个时间内才能够接收到数据。图3描述了数据输入与输出之间的时序关系。

图3 数据输入与输出之间的时序图

2 子模块的设计

2.1 数据加密模块

数据加密是为了将数字内容进行加密,防止不合法的传输和复制,它是内容保护的核心逻辑模块。

HDCP加密好的数据是由HDCP加密机产生的24位伪随机数据流与HDCP保护内容的数据按逐位异或的结果。HDCP加密是一种能同时为身份授权认证和高速传输非压缩视频数据的特殊加密设计。

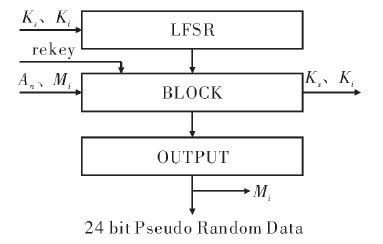

图4 数据加密模块

数据加密模块采用流加密方法实现,流加密的结构如图4所示,主要南3部分组成:

(1)线性反馈移位寄存器(Linear Feedback Shift RegiSTer,LFSR)模块。包括4个不同长度的线性反馈移位寄存器和一个混叠网络。

(2)分组模块。由2个结构非常类似的轮函数B和轮函数K模块组成。

(3)输出功能模块。由基于异或的组合电路组成,在每个时钟脉冲里产生一个24位的伪随机数据。

HDCP控制器根据不同的数据流通方式,分为以下几种不同加密的操作模式:hdcpBlockCipher,hdcp SteamCipher,hdcpRekeyCipher,HDCPRngCipher.在HDCP的协议中对上述几种操作模式都有详细的介绍。HDCPRngCipher操作模式仅为用在发送端中,所以在此不需要支持该种操作模式。

2.2 HDCP接收端控制器

HDCP控制模块控制HDCP接收端的所有操作,它通过个状态机来实现以下功能:

(1)HDCP接收端的状态的控制。

(2)计算Km值,HDCP接收端把Key存储到控制器中。

(3)接收端授权认证状态的转换。

(4)HDCP加密状态的转换:OESS,EESS,两种加密方式。

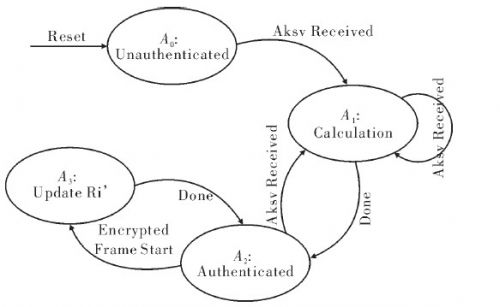

图5描述了授权认证的4个状态之间的关系。状态A0:未授权认证状态;状态A1:计算;状态A2:授权认证完成;状态A3:更新Ri'的值。

图5 授权认证状态图

在Aksv更新信号获得确认后,HDCP控制器根据HDCP发送端的KSV值使用56位二进制的加法来计算Km'值。

在一个时钟内进行20次56位的加法操作可能会产生不能接受的延迟。为了解决这个问题在此提出两种方法来实现该操作。方法一:采用流水线结构,在每个周期里完成一次56位的加法操作,然后在20个周期里完成Km'的最终计算;方法二:使用节约加法器来压缩从2~20的算子,然后执行最终的加法操作。方法二比方法一具有更高的可执行性,但是需要占用更多的资源;方法一相对能节约更多

- 数字内容及其安全(10-26)

- TMS320VC5402 HPI接口与PCI总线接口设计(04-12)