基于MPSoC的以太网接口设计与实现

议转换,如图2所示。该模块包括发送读控制器,发送数据缓存模块和发送写控制器。发送读控制器完成目的地址、源地址和数据类型的数据信息截断,把传播的有效数据写入发送数据缓存模块中,设计通过一个有限状态机结合计数器来完成功能的实现。发送数据缓存模块用一个异步FIFO来承担,同时完成数据8~32位的数据宽度扩展,同时完成跨时钟域数据传输任务。由于该模块数据读入是高时钟频率的8位数据,数据读出是系统时钟频率下的32位数据,数据的流动是由慢到快的传递过程,因此选用一个深度为64的FIFO单元来承担。发送写控制模块通过读取缓存模块中的数据,配置发送数据的有效信息,完成网络数据包格式封装,最后传输至多核系统通信网络资源接口。

2.4 接收模块设计

接收模块承担网络数据包协议到以太网IP核接口协议转换,包含接收写控制器、接收数据缓存模块和接收读控制器。接收写控制器模块设计,通过网络控制信号和FIFO标识信号以及当前状态改变状态机的状态跳转。根据不同状态产生控制信号,实现网络包、配置包、结束包和负载信息的截取,把传播的有效数据写入数据缓冲模块。数据缓存模块把32位网络数据转换到8位宽的以太网控制器接口数据,同时实现数据跨时钟域传输任务。该数据流动方向,速度是由快到慢的过程,结合硬件逻辑资源和任务请求的频度,该设计选用一个深度为1 024,宽度为32的异步FIFO单元来承担。接收读控制器模块通过读取缓存FIFO中数据,配置发送数据的源和目的网卡地址及帧类型,完成以太网数据帧的封装,传输至以太网IP核用户端接口。

3 实验结果

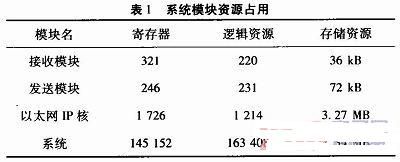

该硬件结构在Xilinx M525开发板上验证实现,FPGA芯片型号为Virtex-5 XC6VLX550T,其中芯片逻辑资源为207360,存储资源为11.39 MB,寄存器资源为207 360,系统硬件在FPGA中资源占用如表1所示。

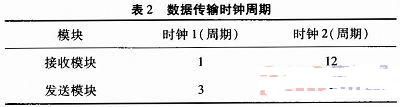

表1是系统设计通过ModelSim功能仿真后,在Xilinx ISE工具上综合后的结果,综合频率高达245.562 MHz。在系统运行中,以太网控制器IP核时钟工作频率在125MHz,系统时钟频率为100MHz。通过仿真和FPGA下载验证后,接口通讯时钟周期统计如表2所示。

通过表2可以看出,以太网接口设计在完成两种协议转换和跨时钟数据传输中,通讯响应时间短,且具有实时和稳定传输,避免了异步时钟在数据传输中的效率问题。

实验测试,把FPGA开发板与PC机通过网线连接,如图6所示。在PC机上编写软件程序,用于发送和接收硬件系统数据,通过修改数据文件,测试不同深度的数据传输。比较发送数据和接收数据文件,判断传输误码率。

实验测试了不同文件大小的数据传输需要时间,统计结果如图7所示。测试结果,发送与接收文件数据,与预期结果一致。通讯时间与数据文件大小近似于线性关系,且传输时间短。以太网接口设计模块为MPSoC承担网络数据通讯,提供了实时和高吞吐率的通讯速度。此外,以太网模块可以用于系统单模块集成调试传输源数据,提高验证效率。以太网接口模块也可以应用于通讯网络,实现系统数据与网络通讯信息的交换。

4 结束语

研究了以太网在MPSoC中的数据通讯,解决了系统在网路通讯中的实时和高吞吐率的数据传输瓶颈。通过该接口与多核系统通讯,可以完成局域网到广域网数据信息传递。

- 以太网接入技术简介(01-09)

- 以太网技术的发展(01-24)

- 基于PC104总线的嵌入式以太网卡设计(01-31)

- 下一代SDH技术发展趋势及应用分析(中)(01-05)

- PLC(电力线通信)技术简介(01-08)

- 电信接入网设备的安全和过压防护测试(01-08)