基于ARM和nRF24L01的无线数据传输系统

1 引言

由于无线数据通信不用布线,快速布局,因此具有有线数据通信无法比拟的便捷性,在特殊场合具有不可替代性。然而,传统的由基本射频集成电路搭建的无线数据通信系统存在电路复杂,成本高,传输速率低,可靠性差等缺点。为此,Nordic公司推出一款工业级内置硬件链路层协议的低成本单芯片nRF24L01型无线收发器件。该器件采用GFSK调制,128个频点自动跳频,片内自动生成报头和CRC校验码,具有出错自动重发功能,这些特性使得由nRF24L0l构建的无线数据传输系统具有成本低,速率高,传输可靠等优点。

2 nRF24L01简介

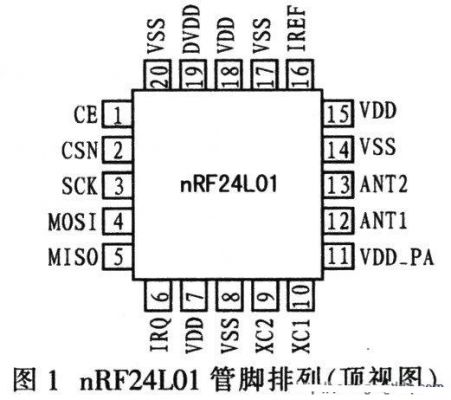

图l给出nRF24L0l的引脚排列。nRF24L01工作于2.4~2.5 GHz ISM频段,内置频率合成器、功率放大器、晶体振荡器、调制器等功能模块,并融合了Enhanced ShoekBurst技术。其中,输出功率、通信频道、自动重发次数等参数可通过编程设置。内置的SPI接口,其速率为0~8Mb/s,MCU通过SPI接口控制nRF 24L0l。nRF24L01的特点如下:①功耗低。能够在以一6 dBm的功率发射时,工作电流只有9 mA;在以0 dBm的功率发射时,工作电流仅11.3 mA;而在接收时,工作电流仅12.3 mA,因此具有掉电和空闲多种低功率工作模式。②体积小,采用QFN20封装。③供电电压为1.9~3.6 V,可方便集成到各种电子器件。

3 LPC214x简介

IPC214x系列是Philips公司的基于ARM7内核的高性能器件,与LPC213x系列器件相兼容,并增加了一些新功能,性能得到了大大的提升。LPC214x系列器件最大特色是内置2kB终端RAM的USB 2.0全速控制器,1个(LPC2141/42)或2个(LPC2144/46/48)10位A/D转换器,多个串行接口,包括2个UART、2个高速I2C总线、SPI和具有缓冲作用及可变数据长度的SSP。LPC214x系列器件采用单电源供电,具有上电复位(POR)和掉电检测(BOD)电路。相对于普通ARM7来说,LPC214x还提升了I/O端口的速度,并且内置8-40 KB的静态RAM和32~512 KB的高速Flash存储器;工作频率高达60MHz;采用超小型LQFP64封装。

4 系统硬件设计

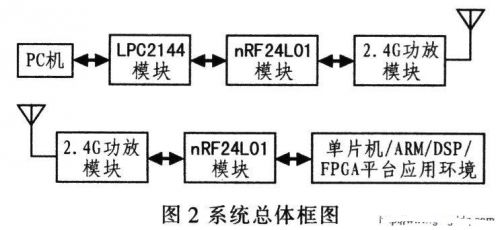

该系统采用模块化设计,主要由LPC2144、nRF24L01、射频功放和天线模块组成。其中,射频功放采用台湾K一BEST公司的2.4 G双向功放模块。图2是系统总体设计图。上位机为PC机,LPC2144与nRF24L01连接,根据需要配置2.4 G功放和增益天线模块。如果配置0.5 W功放和高增益天线,则传输距离可达5~10 km。下位机为嵌入式平台,该嵌入式平台可以是单片机、ARM、DSP和FPGA,nRF24L0l可通过SPI接口直接与嵌入式平台连接。

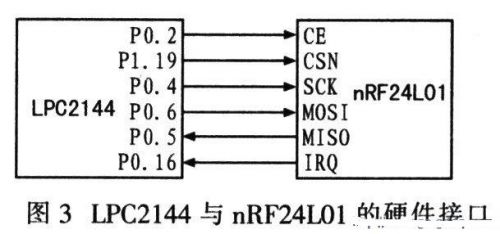

图3给出LPC2144与nRF24L0l的硬件接口设计。配置LPC2144的P0.2、P1.19作为GPIO端口分别与nRF24L0l的CE和CSN连接;配置LPC2144的P0.4、P0.5、P0.6作为SPIO端口分别与nRF24L0l的SCK、MISO、MOSI连接:配置LPC2144的P0.16作为EINT0端口与nRF24L0l的IRQ连接。

5 系统软件设计

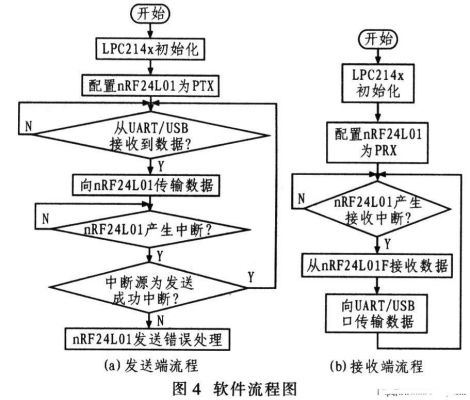

发送端LPC214x完成初始化后,把nRF24L01配置成PTX工作模式。若从上位机接收到数据,则启动nRF24L01发送数据。若发送成功,则产生TX_DS中断;若重发超限,则产生MAX_RT中断;若发送成功,则继续发送,否则进行出错处理。接收端LPC214x完成初始化后,把nRF24L0l配置成PRX工作模式。当正确接收数据时,nRF24L0l产生接收中断标志,LPC214x从nRF24L01读取数据并向下位机发送。图4给出软件流程图。软件开发环境为ADSl.2。

5.1 nRF24L01的初始化

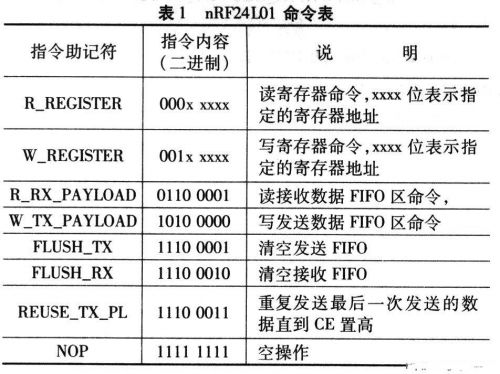

nRF24L01通过SPI接口和外部控制器件如MCU、ARM、DSP进行数据交换,其SPI协议是MSB在前,LSB在后。如果要读写多个字节,先读写低字节。如果外部控制器件没有SPI接口,可用普通I/O接口模拟。这里选用带SPI接口且可方便地与nRF24L0l连接的LPC21440表l给出nRF24L0l的命令表。

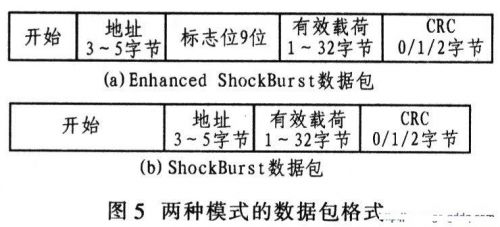

由表可见,通过SPI接口传入nRF24L01的第一个字节是命令字,nRF24L0l的各种命令字都只有一个字节,分为读寄存器、写寄存器、读数据接收缓冲区、写发送数据缓冲区等。在输入任意命令字的同时,MISO输出的都是STATUS寄存器的内容。nRF24L0l的数据传输模式有ShockBurst和Enhanced ShockBurst两种数据包。后者比前者多了一个确认数据传输的信号,保证数据传输的可靠性。该器件内部完成需要高速处理的RF协议,发送数据时只需将数据放入发送数据缓冲区,器件会自行产生前导字符和CRC数据,并将这些数据地址和地址信息、发送数据缓冲区的数据等组成一个数据包发送出去。图5给出两种模式的数据包格式。

现按后一种模式初始化。在配置为接收数据时,nRF24L01接收到数据包后,由硬件解析地址数据和信息数据,当接收到有效信息数据后,在IRQ引脚产生中断,并通知外部处理器读取数据。在

- 基于2.4GHz射频通信的多功能鼠标设计(07-03)

- 基于MCU和nRF24L01的无线通信系统设计(05-29)

- 基于GPRS网络的GPS图形导航仪 (01-05)

- 基于ARM9内核Processor对外部NAND FLASH的控制实现(07-12)

- 基于ARM的局域网IP电话设计(05-11)

- Actel和ARM联合开发专为FPGA应用而优化的高性能32位处理器(02-26)