FPGA研究设计平台为网络发展加速

AEL2005器件。AEL2005是一个带有符合IEEE 802.3aq规范的嵌入式电分散补偿引擎的10Gb以太网物理层收发器。除了常规的10G模式,该物理层器件还能够支持千兆位以太网(1G)模式。在系统侧,这些物理层器件通过一个10Gb连接单元接口(XAUI)连接到FPGA。在1G模式下工作时,其中一个XAUI信道用作串行千兆位介质无关接口(SGMII)。

Virtex-5 FPGA内部提供适当的IP核。对于10Gbps的业务,赛灵思推出了XAUI LogiCORE IP核和10Gb以太网媒体访问控制器(10GEMAC)LogiCORE IP核。对于1G的业务,接口可以直接连接至赛灵思嵌入式三态以太网MAC内核。

PCIe子系统

NetFPGA-10G平台使用开放式组件可移植性基础架构(OpenCPI)作为开发板和计算机主机通过PCIe互联的主要互联实现方式[7]。我们目前支持x8的第一代,将来可能会升级到支持第二代。OpenCPI是一种通用开源框架,用于连接使用不同类型的通信接口、且带宽和时延要求不同的IP模块(串流、字节可寻址等)。就其本质来说,OpenCPI是一种高度可配置的框架,能够为用于快速实现新设计的IP核提供关键性的通信"桥梁"。

OpenCPI为NetFPGA-10G平台带来了一些关键特性。在软件侧,我们能够提供无干扰(clean)DMA接口,用于传输数据(主要是数据包,虽然也有其他类型的信息)以及通过编程的输入/输出控制器件。对于网络应用,我们提供Linux网络驱动程序,将网络接口导出到NetFPGA器件上的每个物理以太网端口上。这样可以让用户空间软件把网络数据包传输到器件上,并且读取设计中任何主机可视寄存器。

在硬件侧,OpenCPI为我们提供了无干扰、甚至多种数据流接口,而且每个接口都可以通过OpenCPI框架进行配置。此外,OpenCPI能够处理主机侧和硬件侧所有的缓存和PCIe事务处理,这样用户就能够集中精力进行特定应用开发,而不必处理器件通信的细节。

扩展接口与配置子系统

扩展接口子系统的目的是让用户通过连接第二块NetFPGA-10G板卡来增加端口密度,比如通过光学子卡来丰富网络接口特性,或者通过高速串行接口连接更多搜索组件,比如基于知识的处理器等。我们将FPGA上的20个GTX收发器取出,然后通过AC耦合传输线连接到两个高速接插件上。这些接插件是为诸如XAUI、PCIe、SATA和Infiniband这样的传输接口设计的,既可以通过匹配接插件直接连接到另一块板卡上,也可以通过电缆组件连接到另一块板卡上。每条传输线经测试双向传输速率均可达到6.5Gbps,从而为进出FPGA提供了一条额外的130Gbps数据路径。

使用不断变大的比特流位宽来配置FPGA,如果器件的配置时间超过PCIe的限制,可能就会出现问题。V5TX240T就会遇到这样的问题:平台闪存器件的存取速度远远低于V5TX240T理论上能够处理的速度,从而带来了瓶颈。作为应对措施,设计人员可以考虑配置部分比特流,并通过并行方式存取平台闪存器件,从而以最大速度配置FPGA。为了提高实现的可能性,我们为板卡配备了两个平台闪存器件,可以通过CPLD连接到FPGA的配置接口。此外,该板卡还支持标准的JTAG编程接口。

FPGA设计

构建成功的开源库的一个关键因素是严格的架构规范以及标准的、抽象且定义准确的接口。实际上,我们认为这些接口对提供一个能够轻松地将大型全球性社区贡献的组件组合在一起的构建块系统具有重要的意义。标准化保证了物理兼容性,物理连接功能之外的清晰定义避免了对接口协议的误解。在理想的情况下,用户可以不对实施内在的知识做详细了解,就可以部署抽象组件。

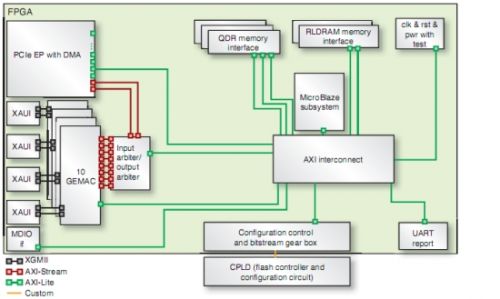

作为完整平台发布的一部分,我们将提供完备的架构规范和带有关键组件的参考设计。这些关键组件包括:

OpenCPI的PCIe端点;

4个XAUI LogiCORE IP模块和4个10G模式下的10GEMAC LogiCORE内核(后者许可协议下使用);

2个基于XAPP852的RLDRAMII存储器控制器;

3个基于MIG3.1的QDRII存储器控制器;

用以检查时钟频率和加电完毕信号,并生成所有所需系统时钟的时钟及复位模块;

针对1G运行模式的三态以太网MAC(TEMAC);

用于配置物理层器件的MDIO接口;

带有能够处理所有管理任务的支持系统的MicroBlaze控制处理器;

UART接口;

配置控制和比特流工具箱,为平台闪存器件提供编程路径;

可将所有输入流量整合成一个数据流的输入仲裁器;

可将流量分配给指定的输出端口的输出仲裁器。

图3显示了这些组件如何互联,以支持10G业务。对数据传输,我们选择了AMBA 4 AXI串流协议。对控制流量,则选择了基于AMBA4 AXI-Lite的接口。

图3:面向10G业务的FPGA设计架构基于AXI协议。

发展现状与未来展望

NetFPGA-10G板卡的设计验证已经完成。一旦完成产品测试平台开

- 以太网接入技术简介(01-09)

- 以太网技术的发展(01-24)

- 基于PC104总线的嵌入式以太网卡设计(01-31)

- 下一代SDH技术发展趋势及应用分析(中)(01-05)

- PLC(电力线通信)技术简介(01-08)

- 电信接入网设备的安全和过压防护测试(01-08)