FPGA研究设计平台为网络发展加速

b/s的PCI Express适配卡,拥有庞大的FPGA架构,能够尽可能多地支持各种应用。如图1所示,该板卡设计以一个大型的赛灵思FPGA器件Virtex-5 XC5VTX240T-2为中心。

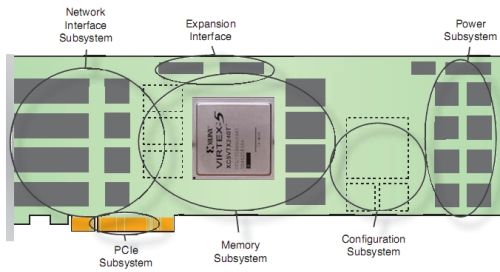

图2:FPGA开发板与网络接口、PCIe、扩展、存储器、配置和电源五个子系统相连。

FPGA与5个子系统相连(见图2)。第一个子系统是网络接口子系统,有4个带有物理层器件的10Gbps以太网接口,用于让网络流量进入FPGA。第二个子系统是存储子系统,其由多个QDRII和RLDRAMII组件构成。I/O主要用于该接口,用来为诸如路由表或包缓存这样的功能提供尽可能高的可用片外带宽。第三个子系统是PCIe子系统。

第四个子系统是扩展接口,用于加载子卡或与其它板卡通信。为此我们把所有剩余的高速串行I/O连接端都接到了两个高速接插件上。第五个子系统是配置子系统,用于FPGA的配置。

总体而言,该板卡就是作为一个双插槽、全尺寸PCIe适配器来实现的。使用两个插槽是出于散热、功耗和高度方面的考虑。与高端图形卡一样,该板卡需要外接ATX电源,因为FPGA在绝对最大负载条件下,功耗可能会超过单槽PCIe允许的50W。不过该板卡也可在服务器环境外独立运行。

存储器子系统

我们设计流程的核心焦点是到SRAM和DRAM组件的接口。因为FPGA器件上的I/O总数限制了可用的片外总带宽,我们必须小心地达成一定的妥协,争取尽量多支持一些应用。要支持从网络监控到安全性、路由、流量管理等各类应用,会带来很大不同的约束。

例如,对外部存储器存取来说,网络监控器会采用一个大型的基于流量的统计表,而且多数情况下可能还需要一个流量分类查找表。对两者的存取都会带来较短的时延,因为流量分类需要对内部依赖性进行多次查找,而流量统计表的更新则一般会覆盖整个读取-修改-写入周期。因此,SRAM是合适的器件选择。不过流量管理器主要需要大量存储空间用于包缓存,通常出于密度要求,还会采用DRAM组件。对外部存储器而言,最后可以考虑使用需要路由表查找和包缓存的IPv4路由器。

总结各种应用的要求,我们认识到某些功能会占用外部存储器带宽,不管是SRAM还是DRAM。包缓存(要求大量存储空间)适合采用DRAM,SRAM则更适用于流量分类搜索存取、路由表查询、基于流量的数据统计表或基于规则的防火墙、用于包缓冲区实现的存储器管理表以及报头队列等。

所有这些功能都需要逐包执行。因此,假定在最恶劣的情况下最小尺寸的包是带20字节开销的64字节,系统需要处理的包率就是大约每秒6000万个包。其次,我们需要将存取做进一步的区分。首先,许多存储器组件,比如QDR SRAM和RLDRAM SIO器件有独立的读/写数据总线。由于存取模式不能假定为系统分布,我们就无法汇聚总的存取带宽,不得不对单独考虑每项业务。

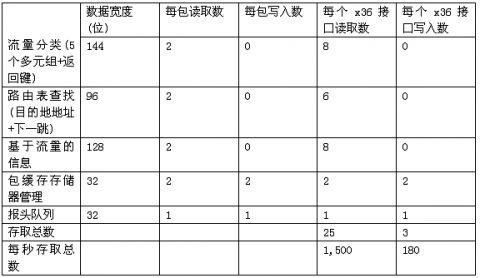

另外,还存在第三类存取,就是"搜索"。搜索可以通过基于TCAM的器件很好地完成,搜索时延固定,且确保能获得搜索结果。不过,出于价格和功耗方面的考虑,以及TCAM会进一步限制I/O使用,我们不准备在我们的开发板上使用TCAM器件。搜索还可以通过诸如决策树、哈希算法和分解法等其他方式来完成,可采用高速缓存也可不用,仅以这些为例。为了便于探讨,我们假定完成一次搜索平均需要近两次读取。鉴于此,以及对数据宽度进行了一些惯常的假设后,我们将要求精简为表1所示。

表1:SRAM带宽需求。

假定接口上的时钟速度为300MHz,那么QDRII接口可以实现每秒2X300=6亿次读/写存取操作。因此,三个QDRII x36位的接口就可以满足我们的所有要求。

对于DRAM存取,我们主要考虑的是包存储的方便程度,仅从存储器中对包进行一次读/写。把包开销从原本进入的2x40Gbps中扣除后,这相对于约62Gbps的存取带宽。用物理资源来衡量,RLDRAMII存取可以实现约97%的效率,而DDR2或DDR3存储设备则可能在40%左右,因此会要求多得多的I/O。因此我们选择了RLDRAMII CIO组件。两个运行在300MHz的64位RLDRAMII接口提供的总带宽可以大致满足这个要求。

网络接口

NetFPGA-10G的网络接口由4个能够以10Gbps或1Gbps以太网链路方式运行的子系统构成。为了最大化平台的利用率和最小化功耗,我们使用了4个增强型小型封装可热插拔(SFP+)模块(cage)作为物理接口。与XENPAK和XFP等其他10G收发器标准相比,SFP+在功耗和尺寸方面有着明显的优势。使用SFP+模块,可以支持一系列接口标准,包括10GBase-LR、10GBase-SR、10GBase-LRM和低成本直联SFP+铜缆(双同轴)。此外,还可以利用针对1Gpbs运行的SFP模块,从而支持1000Base-T或1000Base-X物理标准。

4个SFP+模块每个都通过SFI接口连接到一个NetLogic

- 以太网接入技术简介(01-09)

- 以太网技术的发展(01-24)

- 基于PC104总线的嵌入式以太网卡设计(01-31)

- 下一代SDH技术发展趋势及应用分析(中)(01-05)

- PLC(电力线通信)技术简介(01-08)

- 电信接入网设备的安全和过压防护测试(01-08)