基于FPGA实现的CPCI数据通信

本文设计的系统采用PLX公司生产的CPCI协议转换芯片PCI9054,通过Verilog HDL语言在FPGA中产生相应的控制信号,完成对数据的快速读写,从而实现了与CPCI总线的高速数据通信。

高速数据传输技术是现代信息技术的前沿科技,同时也是整个数据链技术的瓶颈之一,为此技术人员不断地寻找新的方法。CPCI(Compact PCI)总线就是其中一个解决方案。CPCI总线是当前流行的高速嵌入式计算机总线,目前大多数嵌入式计算机系统的接口最终都要经过CPCI总线与计算机内存进行交互。CPCI的总线规范保证了其具有良好的兼容性和可靠性。

1 系统设计

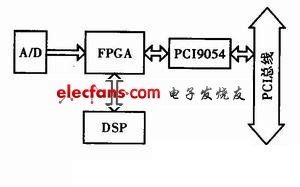

系统主要由PCI9054和FPGA构成,系统结构图以及信号连接如图1所示。通过利用FPGA的可编程性,可实现更多的扩展功能,如与DSP,A/D等不同速率间接高速通信等。协议转换芯片PCI9054的作用就是保证本地数据采集板卡和主CPU板卡之间的数据可以高速准确地传输。

2 PCI9054性能分析

PCI9054是由PLX公司生产的一种基于PCI V2.2总线规范的通用接口芯片。它支持单字节方式和突发方式两种传输方式。其总线端支持32位/33 MHz传输,本地端可以通过突发方式达到最大132 Mbit?s-1的传输速率,并且可以控制改变本地端的总线宽度。

PCI9054可以看做一座建立在CPCI总线和本地用户局部总线之间的桥梁。因为PCI9054具有6个可编程FIFO存储器进行数据缓存,从而保证两者之间数据传输的正确性和实时性。并且PCI9054允许其中任意一端作为主控设备去控制总线,同时另外一端作为目标设备去响应总线。

PCI9054内部具有多个寄存器组,用以对其两端的工作状态和工作方式进行控制。PCI9054对其内部的所有寄存器组和FIFO都行了统一的地址映射,用户可以从两端通过编程访问所有FIFO及寄存器组的每个字节,从而查看两端的工作状态和改变两端的工作方式。

3 PCI9054局部总线的接口设计

整个CPCI接口的设计思路为:FPGA通过桥接芯片PCI9054与CPCI总线连接,其内部使用异步双口RAM来进行高速数据的缓冲,通过使用VerilogHDL语言编程来控制FPGA中的异步双口RAM,以实现系统数据在嵌入式CUP板卡内存与CPCI板卡之间的高速传输。

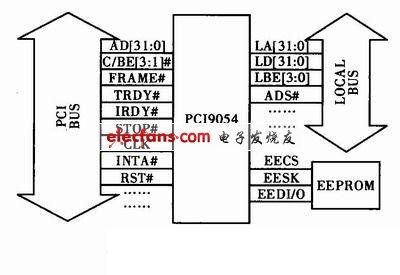

PCI9054提供了3种物理总线接口:CPCI总线接口、LOCAL总线接口和串行EPROM接口。其中CPCI总线接口协议在嵌入式操作系统中的驱动包已经带有,而串行EEPROM的初始化是由PLX公司的PLXMON软件在嵌入式操作系统中进行在线烧写的,所以本系统设计的重点就是关于LOCAL总线接口的控制和传输,其接口电路示意图如图2所示。

PCI9054与本地总线之间的接口称之为LOCAL BUS,是CPCI总线系统设计中十分重要的一环。PCI9054 LOCAL BUS在系统设计中,其总线直接与Alter公司的EP2S90F78014芯片的数据总线相连,同时通过运用Verilog HDL语言编程来实现对双口RAM控制器的功能。

PCI9054 LOCAL BUS有3种工作模式,分别为M、J和C模式。M模式是专为Motorola公司开发和设计的,而另外两种工作模式就应用的比较广泛。其中J模式因为没有LocaL Master,所以它的地址总线和数据线没有分开,从而增加了开发难度。而在C模式下,PCI9054芯片通过片内的逻辑控制可以将CPCI的局部地址和数据总线分开,从而有效地降低了开发难度,并且能灵活地为本地工作时序提供各种工作方式,所以本系统设计方案选择了LOCAL总线的C工作模式,工作频率为40 MHz。

4 局部总线的实现

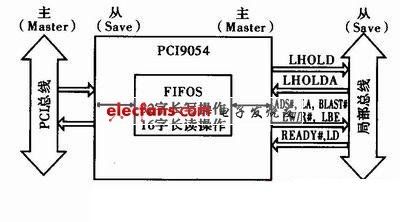

PCI9054支持主模式、从模式和DMA传输方式,根据本系统设计的需求,采用从模式传输方式,即允许CPCI总线上的主设备访问局部总线上的配置寄存器或内存,支持多种模式传输。如图3所示。

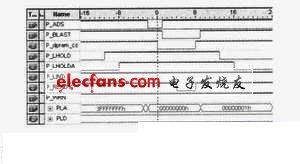

FPGA内部逻辑要设计本地端总线控制模块,实现局部总线的状态控制,同时产生片内的读写时序及地址信号以支持突发传输和单周期传输,因此使用Verilog HDL语言中的状态机来完成上述功能。其状态转换,如图4所示。

5 测试结果

利用SingnalTap采集到的单周期时序传输图,如图5所示。

6 结束语

以PCI9054为核心介绍了CPCI板卡与嵌入式CPU板卡之间高速数据通信系统接口的软硬件设计。PCI9054因其灵活和方便的接口功能,使操作者只需关心LOCAL BUS接口电路的时序设计,并且利用其传输速率高的特性,可以帮助一些对实时性要求较高的系统解决其传输数据的问题。

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)