基于MPEG-4编码的近距离无线视频传输系统

电路

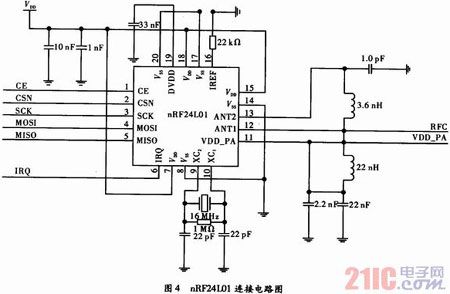

下位机的无线连接采用Nordic Semiconductor公司的nRF24L01。它是一款新型单片射频收发器件,工作于2.4~2.5 GHz ISM频段,采用GFSK调制,硬件集成OSI链路层,最高空中速率达到2Mbit·s-1,采用SPI接口连接控制器。内置频率合成器、功率放大器、晶体振荡器和调制器等功能模块并融合了增强型ShockBurst技术,其输出功率和通信频道可通过程序进行配置,有125个频道。nRF24L01功耗低,在以功率为-6dBm发射时,工作电流只有9mA;接收时,工作电流为12.3mA。

采用SPI接口与控制器FPGA进行连接,负责开机时接收各个器件的配置信息,完成配置后进行视频数据流的无线发送。其中,CE是发射和接收切换引脚,CSN为片选,IRQ为中断信号输出引脚,连接电路图如图4所示。

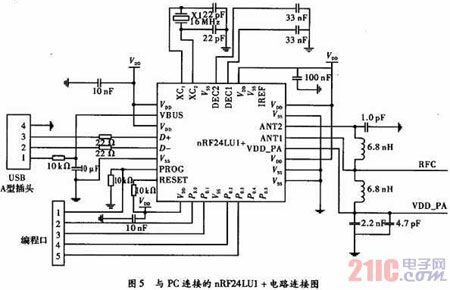

1.2.2 nRF24LU1及其应用电路

nRF24LU1+是Nordic推出的一款将高性能射频收发器与单片USBdongle功能结合起的无线收发芯片,它可实现无线数据到USB数据形式的转换,这样就实现了与PC机的连接。nRF24LU1+内含1个增强型8051MCU内核、无线收发模块、符合全速USB2.0标准的器件控制器。nRF2ALU1+显著地增强了抗宽带干扰和互调失真(IMD)性能。nRF24LU1+芯片需要的外部元件只是低成本的16MHz晶振、去耦电路、匹配网络和天线。USB工作电源电压范围4.0~5.25 V。nRF24LU1+是单片结构,外形尺寸5mm×5mm。它的最高速率2Mbit·s-1,兼容所有nRF24系列芯片;使用Enhanced ShockedBust技术可以实现数据包的自动打包/解包和传输处理;使用MultiCeiver技术可同时支持6个无线装置,频段、输出能量和其他射频参数可通过射频寄存器进行编程调节,电路图如图5所示。

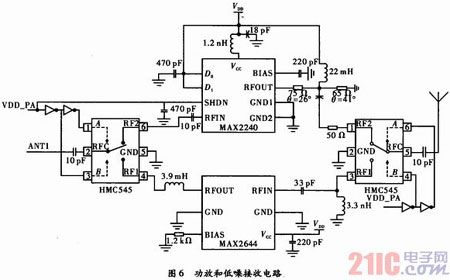

1.2.3 PA和LNA

单独只采用nRF芯片只能近距离的无线通信,为增加无线视频传输的距离,需要加入PA。从增加数据通信距离考虑,还需要增加芯片输入端的接收灵敏度,选用合适的LNA和滤波器成为必然。设计选用Maxim公司的MAX2240和MAX2644,连接电路如图6所示。

MAX224O专为2.4~2.5 GHz频段的应用而设计,符合Bluetooth、HomeRF、802.11标准以及其他FSK调制系统的要求。MAX2644是一款专为WLAN,Bluetooth等工作在2.4GHz频段内的设备设计的高三阶交调点的低噪声放大器。放大电路中,微波开关采用Hittite公司生产的低成本SPDT微波开关,型号HMC545,该开关特别为3G和ISM频段工作的设备设计,其插入损耗仅有0.25dB,采用SOT封装、体积小,可用CMOS或TTL电平控制。利用nRF芯片的VDD_PA引脚控制无线发送和接收的切换。

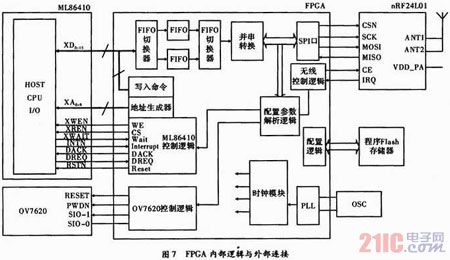

2 控制器FPGA设计

FPGA选用Altrea公司的EP2C8208。其硬件连接电路如图7所示。

3 初始化配置及工作流程

(1)初始化配置方式。

1)OV7620配置。OV7620的控制采用SCCB(Serial Camera Control Bus)协议。它是简化的I2C协议,SIO-1是串行时钟输入线,SIO-0是串行双向数据线,分别相当于I2C协议的SCL和SDA。SCCB的总线时序与I2C基本相同。OV7620功能寄存器的地址为0x00~0x7C。通过设置相应的寄存器,可以使OV7620工作于不同模式。

2)ML86410配置。对ML86410进行配置需要对其寄存器进行配置,通过地址生成器产生地址XA0~9,然后通过数据总线XD0~15对相应寄存器进行写值。由于无线速率最高为2Mbit·s-1,所以一定要对Bits Rate Setting Register(0x18C)进行设置,有可变速率压缩和固定速率压缩两种方式。

3)nRF24L01配置。对nRF24L01进行配置通过对其内部的寄存器进行写值完成,通过SPI总线完成数据的写入。其需要用户配置的寄存器地址为00~17,共18个8bit寄存器,当要进行发送和接收的切换时,同样要写入相应的寄存器值。

(2)工作流程。

1)开机配置:首先测试无线连接,连接成功后由PC端下传参数模式配置命令;下位机接到命令后,由配置参数配置逻辑解析到参数模式后,通过控制逻辑对ML86410和OV7620进行初始化配置,成功后即开始视频采集,失败发送错误到PC端。

2)视频无线发送:视频采集开始后,视频流在ML86410的控制下有序进入FPGA缓冲,缓冲采用乒乓缓冲操作,然后数据经过并串转换,再通过SPI口送入nRF24L01无线发送。

3)视频无线接收:nRF24LU1+接收到视频流后,经过缓冲,即送入USB2.0协议槽通过USB接口传入PC进行显示。

4)视频显示:PC采用VC++编写程序调用Windows自带的视频播放器,同时调入MPEG-4视频流,解码后显示。

4 上位机软件设计

上位机采用VC++编写成熟的视频监控软件,和通用的视频监控软件相同,接收来自USB端口的数据进行解压缩显示即可。效果图如图9所示。

5 结束语

采用具有可靠逻辑功能的FPGA协调MPEG-4视频流到

- 一种基于电力线的家庭以太网络实现方法(10-10)

- 基于DSP和FPGA的机器人声控系统设计与实现 (04-16)

- 面向大众市场的千兆位级收发器(05-04)

- 利用以太网硬件在环路实现高带宽DSP仿真(05-04)

- 采用软处理器IP规避器件过时的挑战(05-04)

- WCDMA系统基带处理的DSP FPGA实现方案(01-02)