基于TMS320DM6437的McBSP与EDMA实现串口通信

TMS320DM6437是专为高性能、低成本视频应用开发的,主频600 MHz,32位定点,采用达芬奇(DaVinci(TM))技术。该器件采用TI第3代超长指令集结构(VelociTI.3)的TMS320C64x+DSP内核,主频可达600 MHz,支持8个8位或4个16位并行MAC运算,峰值处理能力高达4 800MIPS。基于TMS320DM6437诸多特点,这里提出一种实现DSP与FPGA的双向数据交换设计方案,采用TMS320DM6437的McBSP和EDMA实现异步串口通信。 McBSP接口是全双工串行接口,提供收发数据双缓冲以处理连续的数据流,并可独立配置收发部分,接收和发送都可使用独立的帧信号和时钟源。TMS320DM6437有2个独立的McBSP接口(McBSP0和McBSPl)。EDMA可处理该处理器上所有内存单元和外设的数据传输,且不占用DSP时钟周期,EDMA还提供针对McBSP的同步事件,可方便控制数据传输。接收数据时,FPGA的数据通过McBSP传到DSP的DRR寄存器中,触发McBSP接收同步事件,EDMA将数据搬入DSP内存。发送数据时,当EDMA从DSP内存中将数据搬入DSP的DXR寄存器时,利用McBSP发送同步事件,将数据传输给FPGA。

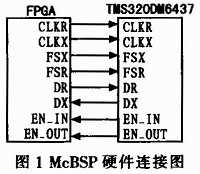

1 硬件接口电路设计

McBsP接口的硬件连接如图1所示。DSP的McBSP接口可由内部时钟发生器或外部器件提供收/发时钟信号(CLKR/CLKX)及收/发帧同步信号(FSR/FSX)。为了简化FPGA内部时序,以上信号均由FPGA提供。图1中的EN_IN、EN_OUT为DSP控制FPGA中McBSP接口的使能信号,它们均与DSP的GPIO相连。当EN_IN为高时,FPGA接收DSP的数据;当EN_OUT为高时,FPGA开始向DSP发送数据。

2 软件程序设计

传统的C6000型DSP对McBSP和EDMA进行操作时,多使用TI公司提供的CSL(Chip Support Library)进行编程操作,由于TMS320DM6437不支持CSL,而是改用PSP(Proeessor Support Package),所以对TMS320DM6437 McBSP接口采用PSP提供的McBSP Driver,主要用McBSP Driver提供的LLC层API进行编程。LLC层提供基于不同平台的驱动核心抽象。在该层可进行寄存器操作,宏定义,并且底层API可直接与硬件通信。

对应的EDMA程序开发则采用EDMA LLD(EDMA low Level Driver)提供的各种库进行编程。LLD实际上包含2个库用于管理EDMA外设:一个是EDMA RM(EDMA Resource Manager),管理所有的EDMA硬件资源以及中断;另一个是EDMA DRV(EDMA Driver),完成所有EDMA相关配置,并且通过RM满足资源需求。当调用DRV层API进行操作时,实际上是通过DRV层API调用RM层API来对EDMA外设寄存器进行直接操作来配置EDMA硬件。

本例中实现DSP和FPGA通信时,McBSP所需的帧同步信号以及时钟信号均由FPGA产生,McBSP发送过来32 bit的数据,DSP内部采用EDMA方式接收数据,McBSP接收同步事件触发EDMA传输。将数据放入DSP片内二级存储器的缓冲区,等待DSP处理。为了保证后写入的数据不会覆盖先写入的还没来得及被DSP处理的数据,片内二级存储器缓冲区采用乒乓缓冲结构。同样,DSP发送32bit数据给FPGA时,也是通过EDMA方式,由McBSP发送同步事件触发EDMA传输。

2.1 McBSP配置

McBSP的开启以及参数配置均采用LLC提供的API以及数据结构完成。但是因为TMS320DM6437的引脚多采用引脚复用,并且GPIO和McBSP引脚复用到一起,由于本例中McBSP帧同步信号是由外部源产生,为了保证能监测到第一个帧同步信号,需先在PINMUX寄存器里将复用的引脚配置成GPIO模式,等检测到帧同步信号后,再将复用的引脚恢复成McBSP模式。

2.1.1 接收数据格式配置

McBSP接收数据格式在数据结构LLC_RcvDataSetup中设置,该数据结构在McBSP Driver提供的头文件llc_mcbsp Type.h中定义,在编译工程文件的时候需包含此头文件。接收数据为单帧数据,一个数据帧长度为4个字节,采用帧同步信号检测模式,不进行压缩,数据传输延迟一个比特,采用McBSP同步事件产生中断。McBSP发送数据格式在数据结构LLC_XmitDatasetup中设置,具体参数和接收数据格式保持一致。M-cBSP帧同步和时钟参数在数据结构LLC_mcbspClkSetup中设置,该结构同样在头文件llc_mcbspType.h中定义。本例中,发送和接收的帧同步信号以及时钟源都由外部产生,接收和发送帧同步都是高电平有效,接收时钟上升沿有效,发送时钟下降沿有效,帧同步脉冲宽度为1bit,脉冲周期为32 bit。

2.1.2 启动McBSP

首先调用MeBSP LLC层API对McBSP接口进行设置,准备接收FPGA传输过来的信号。先调用函数LLC_mcbspOpen,该函数在llc_mcbsp.c中定义,函数原型为LLC_mcbspOpen(LLC_McbspObj*const pMcbspObj,Uint32InstanceId,Int32*pMcbspParam,CSL_Status*pStatus),所需参数分别为用户定义的McBS

TMS320DM6437 McBSP EDMA 串口通信 相关文章:

- 如何实现(电脑)PC机与单片机AT89C51的串行通信(04-19)

- ARM7串口9位方式多机通信的编程技术(05-20)

- RS232接口转USB接口的通信方法(01-12)

- Linux下ARM 和单片机的串口通信设计(04-17)

- GPS定位信息提取及应用(07-31)

- USB虚拟串口通信实现(04-19)