基于压控振荡器(VCO)的高性能锁相环(PLL)设

性结型晶体管输入(BJT)运算放大器,如OP184或OP27等。环路滤波器将会很好地衰减BJT的高输入偏置电流所引起的PFD杂散,而且PLL可以充分利用BJT运算放大器的低噪声电压密度特性。

如果应用要求较小的PFD与环路带宽比(例如在整数N分频频率合成器中),则应折衷考虑噪声与杂散水平;AD820和AD8661可能是较佳选择。

值得注意的是,虽然有源滤波器往往会增加PLL的噪声,但它能够充当缓冲器,在一些特定应用中具有无源滤波器所不及的性能优势。例如,如果VCO调谐端口的泄漏电流较高,导致PFD杂散较高,则可以使用运算放大器来降低杂散水平。运算放大器的低阻抗输出可轻松弥补调谐端口泄漏电流。

设计示例

考虑这样一个例子,其中LO的规格要求如下:

倍频程调谐范围:1000 MHz至2000 MHz

相位噪声要求:–142 dBc/Hz(1 MHz偏移)

杂散:小于–70 dBc

0px; PADDING-BOTTOM: 0px; MARGIN: 0px; PADDING-TOP: 0px">通道间隔:250 kHz

锁定时间:小于2 ms

单电源:15 V或30 V

为在1-GHz频带上工作,同时满足相位噪声要求,有必要使用高压VCO和有源环路滤波器。相位噪声和杂散特性以及单电源限制,将决定运算放大器的选择。为了达到杂散要求,运算放大器必须具有低输入偏置电流,而为了实现最佳相位噪声性能,运算放大器必须具有低电压噪声。选择JFET输入运算放大器可以兼顾以上两个要求,例如AD8661,其输入偏置电流为0.3 pA,电压噪声为12 nV/√Hz。该器件还能处理单电源要求。选择RFMD UMS-2000-A16 VCO来满足倍频程范围要求。

开始设计时,最好利用支持有源滤波器拓扑结构的ADIsimPLLTM工具进行仿真。图3所示为两种推荐的滤波器类型;ADIsimPLL还支持其它配置。

PLL选择ADF4150,它具有整数和小数两种工作模式,提供2/4/8/16/32几种输出分频器选项,可覆盖从2 GHz至31.25 MHz的连续频率。ADF4150与图2所示的ADF4350相似,但前者允许选择外部VCO,适合需要满足更严苛相位噪声要求的应用。在仿真过程中,PLL环路滤波器设置为20 kHz,以期减小运算放大器的噪声贡献,同时使PLL锁定时间小于2 ms。

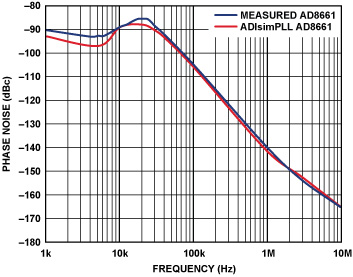

图4所示为采用以下器件的仿真系统与测量系统噪声(dBc)与频率偏移关系曲线:ADF4150 PLL、UMS VCO和基于AD8661的滤波器。两条曲线均显示,由于有源环路滤波器增加的噪声,约20 kHz时出现峰值噪声–90 dBc,不过仍然实现了1 MHz偏移时–142 dBc/Hz的目标。若要降低带内噪声,可以使用OP184或OP27等噪声更低的运算放大器,但杂散会提高;或者将PLL环路带宽降至20 kHz以下。

图4. ADIsimPLL仿真性能与测量性能对比:AD8661用作PLL有源滤波器中的运算放大器

图5显示,使用OP27时性能约改善6 dB。这种情况下,因为环路带宽相对较窄,所以杂散并未显著增加。进一步降低带宽可以改善100 kHz以下偏移的相位噪声,但PLL锁定时间会延长。所有这些权衡考虑均可以在进入实验室设计之前,利用ADIsimPLL模拟进行测试。

图5. 有源环路滤波器中使用AD8661与使用OP27的PLL测量性能对比

爆炸新闻:高压PLL

以上讨论都围绕利用有源滤波器实现低压PLL器件与高压VCO接口而展开。不过,高压PLL已经出现,因而使用有源滤波器的必要性大大降低。例如ADF4113HV PLL,它集成高压电荷泵,归一化相位本底噪声为–212 dBc/Hz。对于该器件,PLL电荷泵输出可以高达15 V,因此VCO之前可以使用更为简单的无源滤波器。

该高压PLL系列产品将会不断扩充,不久将会出现最大电压为30 V的器件,以及具有高压电荷泵的小数N分频PLL。有关产品更新和新产品信息,请访问PLL网站。

集成VCO的宽带宽PLL

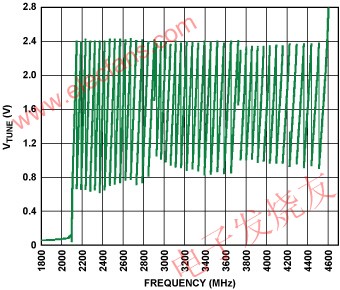

另外可以用完全集成的高性能PLL,例如图2所示的ADF4350等,代替有源滤波器与高压VCO组合。这种情况下,VCO集成在芯片内。采用多频段VCO方法可以避免上述权衡考虑宽调谐范围与低相位噪声的问题。ADF4350片内集成三个独立的VCO,每个VCO均有16个重叠子频段,因而共有48个子频段。每次更新频率时,就会启动自动校准程序,以选择合适的VCO子频段。

这真正体现出从分立式VCO设计转向硅解决方案的优势:在极小的面积上实现非常高的集成度,从而使设计更加灵活。例如,ADF4350同时集成了可编程输出分频器级,可以覆盖从137.5 MHz至4.4 GHz的频率,这对于希望多种频率和标准均采用同一设计的无线电设计师极具吸引力。

ADF4350采用5 mm2 LFCSP封装,而标准VCO封装为12.7 mm2。同时性能水平也接近分立设计;相位噪声在100 kHz偏移时为–114 dBc/Hz,在1 MHz偏移时为–134 dBc/Hz。(返回图2)

图6. ADF4350 VCO中48个不

- 免调节中频VCO: 第一部分: 设计考虑(09-11)