Nios II与CF卡的接口设计

CF卡是最近几年蓬勃发展固态非易失的存储介质,由于CF卡具有携带方便、易于升级、存储量大、抗震性好等优点,在大容量便携式数据存储和传输过程中,CF 有着非常广泛的应用前景,如数码相机、MP3播放器、PDA(个人数字助理)、数字式录音机、笔记本电脑、手提电话、机顶盒等。预计今后在其他领域将有更为广泛的应用。另外CF卡的兼容性佳,不仅同时支持3.3 V和5 V的电压,而且不同的CF卡都可以用单一的机构读写,特别是CF卡升级换代时也可以保证旧设备的兼容性。而纯电子运动的CF卡耗电量很低,仅为IBM 微型硬盘的5%。目前,CF卡容量从最早的2 MB到现今的8 GB,数据传输从最早的5 MB/s发展到现在的20 MB/s。

CF卡由2个基本部分构成:内部控制器和闪存模块。CF卡的闪存模块基本上都使用NAND型闪存,用于存储数据。内部控制器用来实现CF卡与主机的接口以及控制数据的传输。CF卡内部控制器的设计完全模拟硬盘,使用标准的ATA/IDE接口。

CF 的存取方式有3种:PC Card Memory模式、PC Card I/O模式以及True IDE模式。PC Card模式与PCMCIA标准兼容。True IDE模式与ATA标准兼容。

3种方式相比,在True IDE模式下,CF卡与主机通信的信号最少,硬件接口最简单、软件易于实现,因此本设计采用True IDE模式。

2 CF卡接口控制器的寄存器的定义

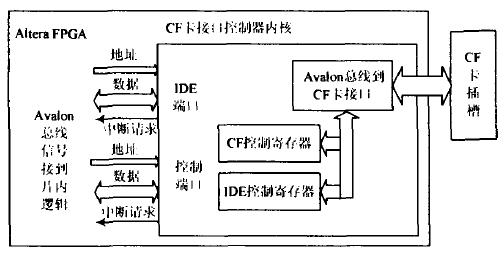

在设计中,采用Altera提供的一个CF接口控制器内核实现CF卡数据的传输.该内核提供一个连接片外CF卡的Avalon总线接口,通过使用适当的时序把Avalon总线信号映射到CF卡,提供了对标准的实IDE模式寄存器的访问,允许设计者在Nios II系统中简易连接就可以使用CF卡。图1所示为CF卡接口控制器内核的结构框图。

图1 CF卡控制器内核结构框图 该内核提供2个Avalon总线从端口.第一个是为了访问CF设备内部的寄存器组,第二个是为了访问控制器内核内部的寄存器文件,CF核提供2个高有效的中断请求输出,一个是CF插入或移除的中断信号,另一个是把设备上的中断信号传送到Avalon主设备。 对于CF卡的操作(如:读/写),其实就是对CF卡控制器的寄存器进行操作。所以,必须对CF卡的寄存器十分熟悉。这些寄存器统称为任务文件(task file)寄存器: (1)数据寄存器(读/写),用于CF卡的读写操作。主机通过该寄存器向CF卡数据缓冲写入或从CF卡数据缓冲读出数据。 (2)错误寄存器(读)和特性寄存器(写) 读操作时,此寄存器为错误寄存器,用于指明错误的原因;写操作时,此寄存器为特性寄存器。 (3)扇区数寄存器(读/写)。用来记录读、写扇区的数目。 (4)扇区号寄存器(读/写),用来记录读、写和校验命令指定的起始扇区号或逻辑块地址(LBA)的BIT7:0。 (5)柱面号寄存器(读/写),用来记录读、写、校验和寻址命令指定的柱面号或LBA的BIT23:8。 (6)驱动器/磁头寄存器(读/写),记录读、写、校验和寻道命令指定的驱动器号、磁头号或LBA的BIT27:24,其中BIT6(LBA)用来设置CF卡扇区的寻址方式(LBA=0,采用CHS模式;LBA=1。采用LBA模式)。 (7)状态寄存器(读)和命令寄存器(写),在读操作时,该寄存器是状态寄存器,指示CF卡控制器执行命令后的状态,读状态寄存器则返回CF卡的当前状态;在写操作时,该寄存器是命令寄存器,接收主机发送给CF卡的控制命令。 3 Nios II处理器与CF卡的硬件接口设计 在Altera公司提供的SoPC软件中对该软核进行配置时,选用Nios II CPU、内部定时器、CF卡接口控制器、SDRAM 控制器、FLASH 存储器接口、LCD 接口和EPCS4串行配置器件控制器接口。其框图如图2所示。

|

- 什么是闪存和缓存 (04-25)

- SD卡以及闪存介质的修复方法 (08-27)

- USB闪存盘驱动器与PIC微控制器的接口设计(04-04)

- 连结USB闪存盘与PIC微控制器的简单方案(04-05)

- 如何选用合适的闪存进行设计?(05-24)

- Spansion发布128Mb MirrorBit SPI闪存 (04-18)